# Domain-Specific Language & Support Tools for High-Level Stream Parallelism

THESIS SUBMITTED FOR THE DEGREE REQUIREMENTS OF:

DOCTOR OF PHILOSOPHY IN COMPUTER SCIENCE

#### Dalvan Griebler

Advisor:

Prof. Dr. Marco Danelutto

Co-advisor:

Prof. Dr. Luiz Gustavo Fernandes

Computer Science Department, Ph.D. Program in Computer Science University of Pisa, Pisa, Italy

Printed: April 28, 2016

## Assessment Committee

#### Assoc. Prof. Marco Aldinucci

Computer Science Department, University of Torino, Torino - Italy

#### Assoc. Prof. José Daniel Garcia

Computer Science and Engineering Department, University Carlos III of Madrid, Madrid - Spain

#### Assoc. Prof. Cesar A. F De Rose

Faculty of Informatics, Computer Science Graduate Program, Pontifical Catholic University of Rio Grande do Sul, Porto Alegre - Brazil

## Abstract

Stream-based systems are representative of several application domains including video, audio, networking, graphic processing, etc. Stream programs may run on different kinds of parallel architectures (desktop, servers, cell phones, and supercomputers) and represent significant workloads on our current computing systems. Nevertheless, most of them are still not parallelized. Moreover, when new software has to be developed, programmers often face a trade-off between coding productivity, code portability, and performance. To solve this problem, we provide a new Domain-Specific Language (DSL) that naturally/on-the-fly captures and represents parallelism for stream-based applications. The aim is to offer a set of attributes (through annotations) that preserves the program's source code and is not architecture-dependent for annotating parallelism. We used the C++ attribute mechanism to design a "de-facto" standard C++ embedded DSL named SPar. However, the implementation of DSLs using compiler-based tools is difficult, complicated, and usually requires a significant learning curve. This is even harder for those who are not familiar with compiler technology. Therefore, our motivation is to simplify this path for other researchers (experts in their domain) with support tools (our tool is CINCLE) to create high-level and productive DSLs through powerful and aggressive source-to-source transformations. In fact, parallel programmers can use their expertise without having to design and implement low-level code. The main goal of this thesis was to create a DSL and support tools for high-level stream parallelism in the context of a programming framework that is compiler-based and domain-oriented. Thus, we implemented SPar using CINCLE. SPar supports the software developer with productivity, performance, and code portability while CINCLE provides sufficient support to generate new DSLs. Also, SPar targets source-to-source transformation producing parallel pattern code built on top of FastFlow and MPI. Finally, we provide a full set of experiments showing that SPar provides better coding productivity without significant performance degradation in multi-core systems as well as transformation rules that are able to achieve code portability (for cluster architectures) through its generalized attributes.

## SOMMARIO

I sistemi che elaborano stream di dati vengono utilizzati in svariati domini applicativi che includono, per esempio, quelli per il trattamento di video, audio, per la gestione delle reti e per la grafica. I programmi che elaborano stream di dati possono essere utilizzati e fatti girare su diversi tipi di architetture (dai telefoni cellulari, ai sistemi desktop e server, ai super computer) e di solito hanno unpeso computazionale significativo. Molti di questi programmi sono ancora sequenziali. Inoltre, nel caso di sviluppo di nuove applicazioni su stream, i programmatori devono impegnarsi a fondo per trovare un buon compromesso fra programmabilità, produttività, portabilità del codice e prestazioni. Per risolvere i problemi relativi alla parallelizzazione e allo sviluppo di applicazioni su stream, abbiamo messo a disposizione un linguaggio di programmazione domain-specific (DSL) che cattura e rappresenta gli aspetti legati al parallelismo in applicazioni su stream. Lo scopo è quello di offrire una serie di attributi (annotazioni) che, modellando gli aspetti relativi al calcolo parallelo dei dati sugli stream, permettano di preservare il codice originale e non dipendano dall'architettura considerata. Abbiamo utilizzato gli attributi C++11 per mettere a disposizione un DSL "interno" chiamato SPar pienamente conforme allo standard C++. L'implementazione di un DSL mediante compilatori è un processo complicato e che normalmente richiede un lungo processo di apprendimento relativo agli strumenti utilizzati; il processo è tanto più lungo quanto meno familiari si è rispetto alla tecnologia degli strumenti di compilazione. La motivazione che ci ha spinto a questo lavoro è dunque quella di semplificare la vita ad altri ricercatori (esperti del loro specifico dominio applicativo) mettendo a disposizione strumenti (CINCLE) che permettono la realizzazione di DSL di alto livello attraverso trasformazioni di codice source-to-source efficaci e potenti. Tramite gli strumenti messi a disposizione i programmatori di applicazioni parallele possono utilizzare la loro esperienza senza dover progettare e implementare codice di basso livello. Lo scopo principale di questa tesi è quello di creare un DSL ad alto livello di astrazione per computazioni parallele su stream e di metterne a disposizione gli strumenti di supporto in un framework basato su compilatori e orientato al dominio delle applicazioni stream parallel. Si è arrivati così alla realizzazione di SPar basata su CINCLE. SPar mette a disposizione dello sviluppatore di applicazioni un ambiente ad alta produttività, alte prestazioni e che garantisce la portabilità del codice, mentre CINCLE mette a disposizione il supporto necessario a generare nuovi DSL. SPar mette a disposizione trasformazioni source-to-source che producono codice parallelo basato su pattern in FastFlow e MPI. Alla fine della tesi presentiamo una serie completa di esperimenti che mostrano sia come SPar fornisca una buona produttività nella progettazione e realizzazione delle applicazioni parallele su stream senza al contempo portare a un degrado nelle prestazioni su sistemi multi core, sia come le regole di trasformazione utilizzate per la generazione del codice FastFlow o MPI permettano di realizzare laiv portabilità del codice basato su attributi su architetture di tipo diverso.

Sistemas baseados em fluxo contínuo de dados representam diversos domínios de aplicações, por exemplo, video, áudio, processamento gráfico e de rede, etc. Os programas que processam um fluxo contínuo de dados podem executar em diferentes tipos de arquiteturas paralelas (estações de trabalho, servidores, celulares e supercomputadores) e representam cargas de trabalho significantes em nossos sistemas computacionais atuais. Mesmo assim, a maioria deles ainda não é paralelizado. Além disso, quando um novo software precisa ser desenvolvido, os programadores necessitam lidar com soluções que oferecem pouca produtividade de código, portabilidade de código e desempenho. Para resolver este problema, estamos oferecendo uma nova linguagem específica de domínio (DSL), que naturalmente captura e representa o paralelismo para aplicações baseadas em fluxo contínuo de dados. O objetivo é oferecer um conjunto de atributos (através de anotações) que preservam o código fonte do programa e não é dependente de arquitetura para anotar o paralelismo. Neste estudo foi usado o mecanismo de atributos do C++ para projetar uma DSL embarcada e padronizada com a linguagem hospedeira, que foi nomeada como SPar. No entanto, a implementação de DSLs usando ferramentas baseadas em compiladores é difícil, complicado e geralmente requer uma curva de aprendizagem significativa. Isto é ainda mais difícil para aqueles que não são familiarizados com uma tecnologia de compiladores. Portanto, a motivação é simplificar este caminho para outros pesquisadores (sabedores do seu domínio) com ferramentas de apoio (a ferramenta é chamada de CINCLE) para implementar DSLs produtivas e de alto nível através de poderosas e agressivas transformações de fonte para fonte. Na verdade, desenvolvedores que criam programas com paralelismo podem usar suas habilidades sem ter que projetar e implementar o código de baixo nível. O principal objetivo desta tese foi criar uma DSL e ferramentas de apoio para paralelismo de fluxo contínuo de alto nível no contexto de um framework de programação que é baseado em compilador e orientado a domínio. Assim, SPar foi criado usando CINCLE. SPar oferece apoio ao desenvolvedor de software com produtividade, desempenho e portabilidade de código, enquanto CINCLE oferece o apoio necessário para gerar novas DSLs. Também, SPar mira transformação de fonte para fonte produzindo código de padrões paralelos no topo de FastFlow e MPI. Por fim, temos um conjunto completo de experimentos demonstrando que SPar oferece melhor produtividade de código sem degradar significativamente o desempenho em sistemas multi-core bem como regras de transformações que são capazes de atingir a portabilidade de código (para arquiteturas multi-computador) através dos seus atributos genéricos.

## ACKNOWLEDGEMENTS

First of all, I would like to thank God for this opportunity and support given to me during my whole life. Second, all the people that were around me, that were part of this project. Their patience and help were fundamental. I especially thank my advisors for supporting and guiding this research as well as their availability to discuss and teach.

Research in parallel computing has been necessary aiming to achieve high-performance and exploit parallelism in Cluster, Multi-Core, and General-Purpose Graphic Processing Unit (GPGPU) architectures. We have had the pleasure of seeing the growth of new programming models, methodologies, and programming interfaces for the efficient use of such a great amount of computational power. These contributions have supported discoveries in many scientific research fields including molecular dynamic simulations, data analysis, weather forecasting, and aerodynamics simulations.

Even though several new interesting results have been achieved in parallel computing over the last two decades, more work still needs to be done to achieve higher level programming abstractions, coding productivity, better performance, etc. At the moment, exploiting parallelism is still a challenging task that requires significant expertise in parallel programming. For example, a software engineer must have a great deal of knowledge of one or more of the following aspects along with their respective challenges:

- 1. Hardware infrastructure: Optimization is not always abstracted by using programming frameworks. Thus, memory locality, cache misses, network communication, thread/process affinity, storage implementation, and energy consumption will significantly impact the application's performance and are heavily dependent on hardware optimized features.

- 2. **Programming models:** May be used and carefully optimized in different ways for synchronizing and communicating threads or processes. For instance, in shared memory, one must pay attention to race conditions and deadlocks. In message passing, deadlocks and process synchronizations are the most important. For heterogeneous programming, there are thread synchronization and memory copy between CPU and GPU. Finally, hybrid programming is a challenge for the efficient use of message passing and shared memory models.

- 3. **Problem decomposition:** Is the computational mapping in the processors. One must identify concurrent works and decompose them by using task, data, DataFlow, and stream parallelism.

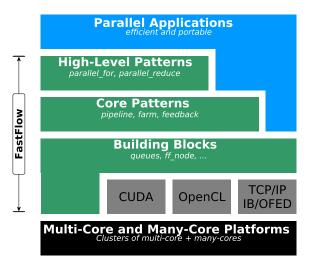

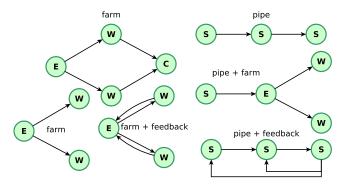

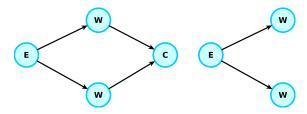

- 4. **Parallelism strategies:** Are algorithmic skeletons and design patterns for helping programmers to express parallelism. Usually strategies like farm, pipeline, and MapReduce are already provided in programming frameworks through a template library such as FastFlow or TBB.

- 5. Load balancing: Refers to workloads being partitioned across CPUs. In general, a static and dynamic approach may be adopted. Some frameworks implement these primitives in their runtime system, such as OpenMP. However, it is up to the user to define appropriate chunk sizes so that the work will be balanced.

- 6. Scheduling policies: These are used to efficiently distribute jobs among CPUs. Most of the frameworks do not offer the user the freedom to implement their own scheduler, instead they must use one of the pre-defined scheduling policies such as round robin, fixed priority, FIFO or EDF. In some applications, if the runtime scheduler is not efficient enough, an ad-hoc scheduling policy must be implemented.

- 7. **Different Programming frameworks:** These may be used to help developers express parallelism. There are several available such as OpenMP, TBB, MPI, OpenCL, X10, CUDA, and FastFlow. They are not able to abstract all the previous aspects and most of them are designed for a particular programming model.

These items are only a partial list of the problems and possibilities regarding parallel programming. We could also highlight many challenges related to each one of these items that are still being researched to improve performance and abstraction. Moreover, some researchers prefer to focus on a specific set of aspects, concerning a specific architecture. Focusing on a specific domain helps people to achieve better and more efficient solutions. Thus, when looking at the current state-of-the-art, only experts are able to efficiently parallelize their applications. It is clear that abstractions are also needed for software engineers and application developers because they already have to face the complexities of their domain.

This research problem initially prompted my Master's thesis, which proposed an external Domain-Specific Language for Pattern-Oriented Parallel Programming (named DSL-POPP) [Gri12]. The first version provided building block annotations for implementing master/slave-like computations on multi-core platforms. The results demonstrated significant programming effort reduction without performance losses [GAF14]. During the Ph.D., a second version was released, which supported pipeline-like parallelization [GF13]. Even though the results also demonstrated good performance, some abstraction limitations were discovered that considerably changed the subsequent domain and interface [GDTF15]. In general, many other problems arose from this initial research which made the work more advanced, primarily regarding high-level parallelism and DSL design.

Another related domain-specific language for MapReduce-like computations was proposed in [AGLF15a], which had the same principles as DSL-POPP. However, a completely new and unified programming language was created. The goal was to avoid MapReduce application developers from having to implement their code twice in order to run in distributed and shared memory environments. The performance results based on the transformation rules were efficient and the DSL significantly reduced the programming effort. The results of this collaboration further reinforced the importance of having a high-level abstraction to avoid architecture details (Chapter 6).

Additionally, the experience with the external DSL also demonstrated many advantages for coding productivity, as presented before in DSL-POPP [AGLF15b].

These past experiences were fundamental to the planning and development of the proposed programming framework (Chapter 3). DSL-POPP was initially an external interface and a cross-compiler was manually developed. Since the goal was always to preserve the sequential source code by only adding annotations, developers still had to learn another language when using it. Consequently, the drawback was that it did not preserve the syntax of the C language. Also, as the compiler did not follow any standardization and due to its internal customization for a specific pattern, there was no modularity for adding new annotations and features. In the literature there are only a small set of tools for creating internal DSLs in C/C++ (Clang and GCC plugins). Most of them only extend language capabilities and their internal implementations vary. Thus, there is a significant learning curve to implement a solution, which nonetheless has more or less the same limitations found previously in DSL-POPP.

One of the design goals of our framework is modularity and simplicity for building high-level C/C++ embedded DSLs. The challenge is to allow parallel programming experts to provide custom annotations by using the standard C++ mechanism so that parallel code can be automatically generated. Although this mechanism (C++11 attributes) was released in 2011, GCC plugins (compilation time callbacks for the AST) and Clang (compiler front-end on top of LLVM) are still difficult to customize and create new attribute annotations.

Another limitation is that these tools do not allow for transformations in the Abstract Syntax Tree (AST). Thus, there are only two options: use pretty print parallel code or build another AST when parsing the code so that modifications will be performed in the new one. GCC plugin constraints and complexities are justified by the C/C++ flexibility and its design goal is not for source-to-source code transformations/generations. On the other hand, Clang provides better modularity with functionalities for parsing AST and creating another one, but it still requires significant expertise in its front-end library and compilers.

The major difference between the annotation-based proposal is that instead of using pragma annotations, C++11 attributes are not preprocessing annotations and are fully represented in the AST with other C/C++ statements. Consequently, they are parsed in the AST, giving more power to the language developer to perform transformations. All of these aspects demonstrate that a Compiler Infrastructure for building New C/C++ Language Extensions was necessary, which is referred to in the text as CINCLE<sup>i</sup> (Chapter 4). This contribution allows one to achieve high-level parallelism abstractions, as will be presented in Chapter 5 by implementing a DSL for stream parallelism (SPar).

<sup>&</sup>lt;sup>i</sup>This is also the name of the bird that lives on shallow streams in Italy, France and Germany

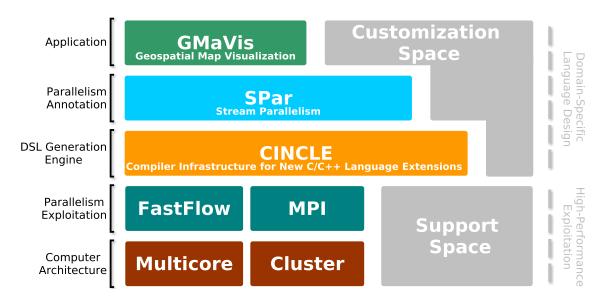

Stream domain was chosen as the annotation interface because it is interesting, widely used, simple enough, general, and suitable for teaching purposes. Moreover, it helps us to address another new perspective and allows application-level DSL designers to integrate automatic parallelization through SPar. Vertical validation of the framework was done through a DSL for geospatial data visualization targeting multi-core parallelism [LGMF15] [Led16]. When compared with TBB, SPar was able to increase coding productivity by 30% ii without significant performance losses.

This research is also a collaboration with the University of Pisa, providing inspiration for this work (e.g. such as the adoption of the stream parallelism domain and the use of the C++ annotation mechanism). The major ideas come from EU (European Union) projects such as REPARA<sup>iii</sup> (annotation mechanism) and the open source project at UNIPI such as FastFlow<sup>iv</sup> (stream parallelism). Both projects have justified and inspired some of our work.

In this thesis, we will provide a new programming framework perspective for high-level stream parallelism. Our motivation is to contribute to the scientific community with a high-level parallelism design with support tools for generating new embedded C++ DSLs. It primarily supports users to build custom and standardized annotation-based interfaces to perform powerful source-to-source transformations.

Another contribution is to enable productive stream parallelism by preserving the sequential source code of the application. In this case, we prototyped a new DSL with suitable attributes at the stream domain level by using our designed infrastructure, which also became the use case to illustrate its capabilities and robustness. Moreover, as a consequence of the generalized transformation rules created, our DSL seeks to support code portability by performing automatic parallel code generation for multi-cores and clusters.

<sup>&</sup>lt;sup>ii</sup>Measuring the source lines of code.

iiihttp://repara-project.eu/

ivhttp://calvados.di.unipi.it/

## LIST OF PAPERS

- 1. Towards a Domain-Specific Language for Patterns-Oriented Parallel Programming. Programming Languages 17th Brazilian Symposium SBLP [GF13].

- 2. Performance and Usability Evaluation of a Pattern-Oriented Parallel Programming Interface for Multi-Core Architectures. The 26th International Conference on Software Engineering & Knowledge Engineering [GAF14].

- 3. An Embedded C++ Domain-Specific Language for Stream Parallelism. International Conference on Parallel Computing (ParCo 2015) [GDTF15].

- 4. A Unified MapReduce Domain-Specific Language for Distributed and Shared Memory Architectures. The 27th International Conference on Software Engineering & Knowledge Engineering [AGLF15a].

- 5. Coding Productivity in MapReduce Applications for Distributed and Shared Memory Architectures. *International Journal of Software Engineering and Knowledge Engineering* [AGLF15b].

- 6. Towards a Domain-Specific Language for Geospatial Data Visualization Maps with Big Data Sets. ACS/IEEE International Conference on Computer Systems and Applications [LGMF15].

## LIST OF ABBREVIATIONS

**SPar** Stream Parallelism

**CINCLE** Compiler Infrastructure for New C/C++ Language Extensions

**AST** Abstract Syntax Tree

**GCC** GNU C Compiler

**GPGPU** General-Purpose Graphics Processing Unit

**GPU** General-Purpose Graphics Processing Unit

**CPU** Central Processing Unit

**FIFO** First In, First Out

**EDF** Earliest Deadline First

**OpenMP** Open MultiProcessing

**TBB** Threading Building Blocks

**MPI** Message Passing Interface

**OpenCL** Open Computing Language

**CUDA** Compute Unified Device Architecture

**UNIPI** University of Pisa

**REPARA** Reengineering and Enabling Performance and poweR of Applications

**DSL** Domain-Specific Language

**IoT** Internet of Things

**DAG** Directed Acyclic Graph

**PPL** Pervasive Parallelism Laboratory

**IR** Internal Representation

**API** Application Program Interface

**PIPS** Parallelization Infrastructure for Parallel Systems

**RTL** Register Transfer Language

**LLVM** Low-Level Virtual Machine

**EDG** Edison Design Group

**ANTRL** Another Tool For Language Recognition

**IDE** Integrated Development Environment

FPGA Field-Programmable Gate Array

**DSP** Digital Signal Processor

**MIT** Massachusetts Institute of Technology

APGAS Asynchronous Partitioned Global Address Space

**SLOC** Source Lines of Code

# Contents

| Lis | st of | Figures  | 5                                       | xiii       |

|-----|-------|----------|-----------------------------------------|------------|

| Lis | st of | Tables   |                                         | xvii       |

| ı   | Sce   | enario   |                                         | 1          |

| 1   | Intro | oductio  | on                                      | 3          |

|     | 1.1   | Conte    | xtualization                            | 4          |

|     |       | 1.1.1    | Perspectives on High-Level Parallelism  | 4          |

|     |       | 1.1.2    | Stream Parallelism Domain               | 7          |

|     | 1.2   | Goals    |                                         | 13         |

|     | 1.3   | Contri   | ibutions                                | 14         |

|     | 1.4   | Outlin   | ne                                      | 14         |

| 2   | Rela  | ated W   | ork                                     | 17         |

|     | 2.1   | High-I   | Level Parallelism                       | 18         |

|     |       | 2.1.1    | REPARA Research Project                 |            |

|     |       | 2.1.2    | Stanford Pervasive Parallelism Research |            |

|     |       | 2.1.3    | Discussion                              | 21         |

|     | 2.2   | C/C+     | + DSL Design Space                      |            |

|     |       | 2.2.1    | Cetus                                   |            |

|     |       | 2.2.2    | PIPS                                    | 23         |

|     |       | 2.2.3    | GCC-Plugins                             |            |

|     |       | 2.2.4    | Clang                                   | 26         |

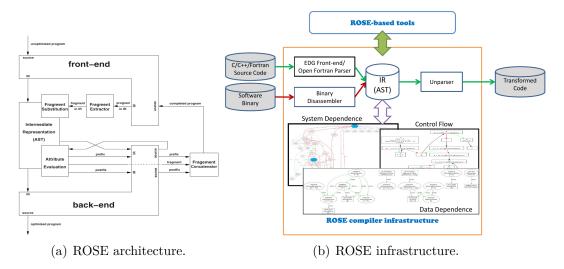

|     |       | 2.2.5    | ROSE                                    | 27         |

|     |       | 2.2.6    | Comparison                              | 28         |

|     | 2.3   | Paralle  | el Programming Frameworks               | 30         |

|     |       | 2.3.1    | Stream-Based                            | 31         |

|     |       | 2.3.2    | Annotation-Based                        |            |

|     |       | 2.3.3    | General-Purpose Frameworks              | 34         |

|     |       | 2.3.4    | Comparison                              | 35         |

|     | 2.4   | Conclu   | uding Remarks                           | 38         |

| Ш   | Co    | ontrib   | utions                                  | 39         |

| 3   | Ove   | rvio:: - | of the Contributions                    | 41         |

| J   | 3.1   |          | luction                                 |            |

|     | 3.2   |          | rogramming Framework                    |            |

|     | 3.3   |          | npiler-Based Infrastructure             |            |

|     | 0.0   | II OUL   |                                         | <b>±</b> 0 |

<u>x</u> Contents

|   | 3.4   | High-Level and Productive Stream Parallelism                     | 46 |

|---|-------|------------------------------------------------------------------|----|

|   | 3.5   | Introducing Code Portability for Multi-Core and Clusters         | 47 |

| 4 | CIN   | CLE: A Compiler Infrastructure for New C/C++ Language Extensions | 49 |

|   | 4.1   | Introduction                                                     | 50 |

|   | 4.2   | Original Contribution                                            | 51 |

|   | 4.3   | Implementation Design Goals                                      | 52 |

|   | 4.4   | The CINCLE Infrastructure                                        | 54 |

|   | 4.5   | CINCLE Front-End                                                 | 55 |

|   | 4.6   | CINCLE Middle-End                                                | 56 |

|   | 4.7   | CINCLE Back-End                                                  | 57 |

|   | 4.8   | Supporting New Language Extensions                               | 59 |

|   | 4.9   | Real Use Cases                                                   | 60 |

|   | 4.10  | Summary                                                          | 63 |

| 5 | SPa   | r: an Embedded C++ DSL for Stream Parallelism                    | 65 |

|   | 5.1   | Introduction                                                     | 66 |

|   | 5.2   | Original Contributions                                           | 67 |

|   | 5.3   | Design Goals                                                     | 67 |

|   | 5.4   | SPar DSL: Syntax and Semantics                                   | 69 |

|   |       | 5.4.1 ToStream                                                   | 69 |

|   |       | 5.4.2 Stage                                                      | 71 |

|   |       | 5.4.3 Input                                                      | 72 |

|   |       | 5.4.4 Output                                                     | 72 |

|   |       | 5.4.5 Replicate                                                  | 73 |

|   | 5.5   | Methodology Schema: How to Annotate                              | 74 |

|   | 5.6   | Examples and Good Practices                                      | 75 |

|   | 5.7   | SPar Compiler                                                    | 81 |

|   | 5.8   | SPar Internals                                                   | 82 |

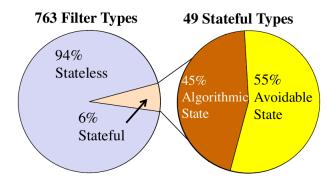

|   | 5.9   | Annotation Statistics on Real Use Cases                          | 83 |

|   | 5.10  | Summary                                                          | 84 |

| 6 | Intro | oducing Code Portability for Multi-Core and Cluster              | 85 |

|   | 6.1   | Introduction                                                     | 86 |

|   | 6.2   | Original Contribution                                            | 86 |

|   | 6.3   | Parallel Patterns in a Nutshell                                  | 87 |

|   | 6.4   | Multi-Core Runtime (FastFlow)                                    | 89 |

|   | 6.5   | Cluster Runtime (MPI Boost)                                      | 91 |

|   |       |                                                                  | 91 |

|   |       | 6.5.2 Pipeline                                                   | 92 |

|   |       | 6.5.3 Pattern Compositions                                       | 93 |

|   | 6.6   | Generalized Transformation Rules                                 | 94 |

Contents

|    | 6.7  | Source-to-Source Transformations Use Cases | . 98  |

|----|------|--------------------------------------------|-------|

|    |      | 6.7.1 Transformations for Multi-Core       | . 98  |

|    |      | 6.7.2 Transformations for Cluster          | . 100 |

|    | 6.8  | Summary                                    | . 102 |

|    |      |                                            |       |

| Ш  | I E  | xperiments                                 | 103   |

| 7  | Resi | ults                                       | 105   |

|    | 7.1  | Introduction                               | . 107 |

|    | 7.2  | Experimental Methodology                   | . 107 |

|    |      | 7.2.1 Benchmarking Setup                   | . 107 |

|    |      | 7.2.2 Tests Environment                    | . 108 |

|    |      | 7.2.3 Performance Evaluation               | . 109 |

|    |      | 7.2.4 Coding Productivity Instrumentation  |       |

|    | 7.3  | Multi-Core Environment                     | . 111 |

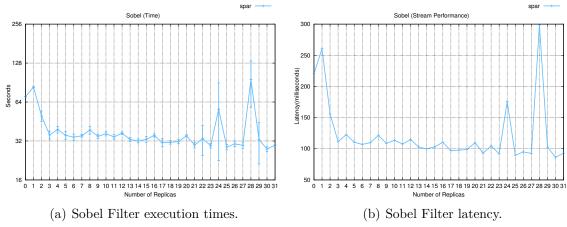

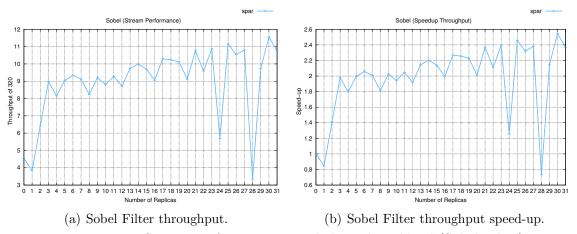

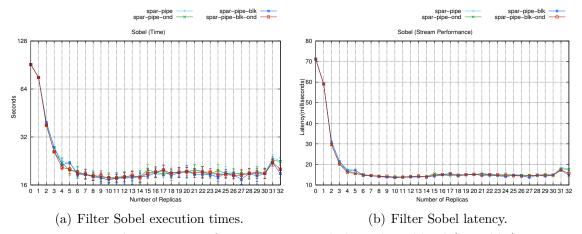

|    |      | 7.3.1 Sobel Filter                         | . 111 |

|    |      | 7.3.2 Video OpenCV                         | . 126 |

|    |      | 7.3.3 Mandelbrot Set                       | . 133 |

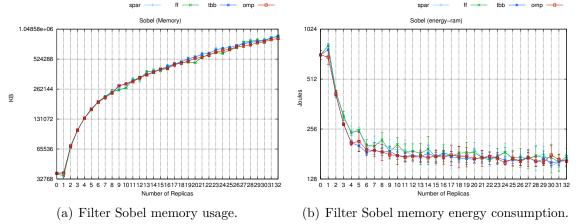

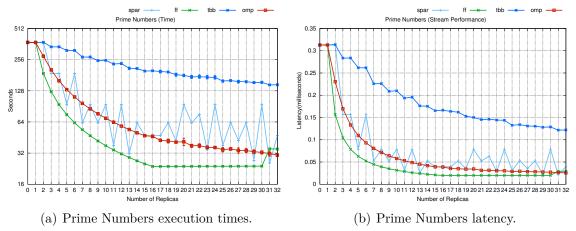

|    |      | 7.3.4 Prime Numbers                        | . 140 |

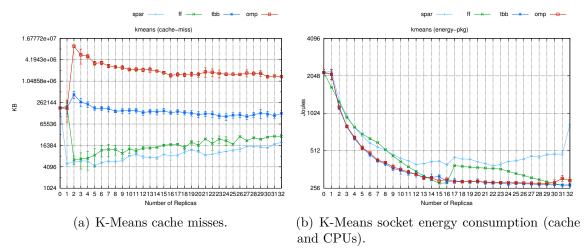

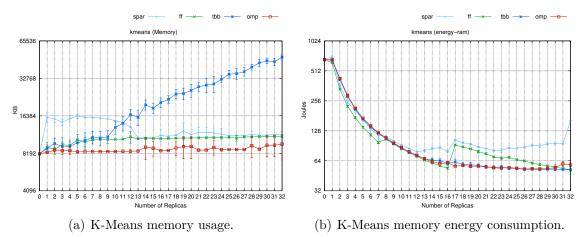

|    |      | 7.3.5 K-Means                              | . 148 |

|    | 7.4  | Cluster Environment                        | . 156 |

|    |      | 7.4.1 Sobel Filter                         | . 156 |

|    |      | 7.4.2 Prime Number                         | . 157 |

|    | 7.5  | Summary                                    | . 159 |

|    | _    |                                            |       |

| IV |      | Discussions                                | 161   |

| 8  | Con  | clusions                                   | 163   |

|    | 8.1  | Overview                                   | . 164 |

|    | 8.2  | Assessments                                | . 165 |

|    | 8.3  | Limitations                                | . 166 |

|    | 8.4  | Considerations                             | . 166 |

| 9  | Futi | ure Work                                   | 169   |

|    | 9.1  | Programming Framework                      | . 170 |

|    |      | 9.1.1 CINCLE                               | . 170 |

|    |      | 9.1.2 SPar                                 | . 170 |

|    |      | 9.1.3 Transformation Rules                 | . 171 |

|    | 9.2  | Experiments                                | . 172 |

xii Contents

| V  | Co                 | omple  | ments                                 | 173   |  |

|----|--------------------|--------|---------------------------------------|-------|--|

| 10 | 0 Bibliography 175 |        |                                       |       |  |

| Α  | Арр                | endix  |                                       | 189   |  |

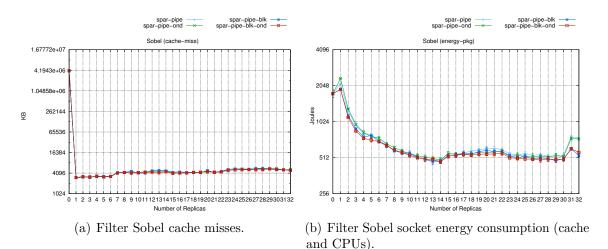

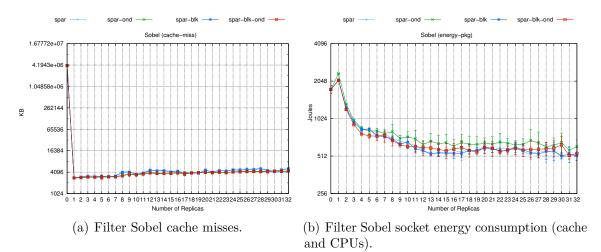

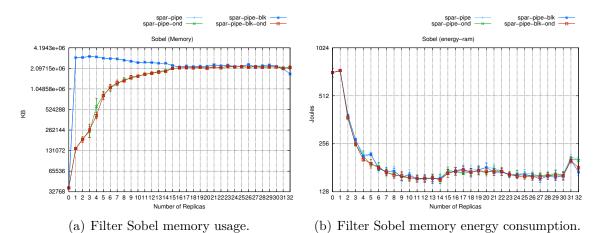

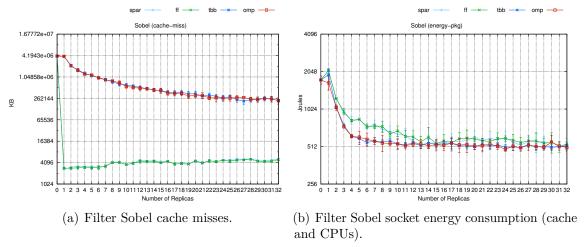

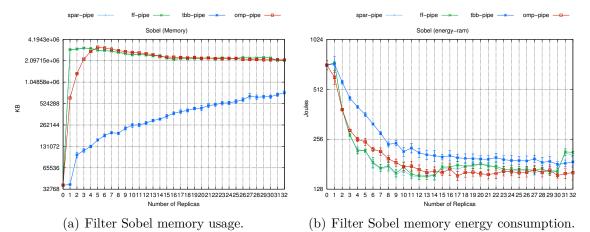

|    | A.1                | Compl  | lementary Results on Multi-Core       | . 190 |  |

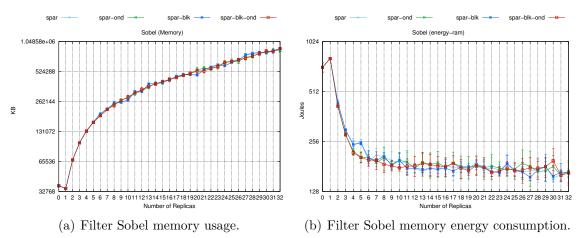

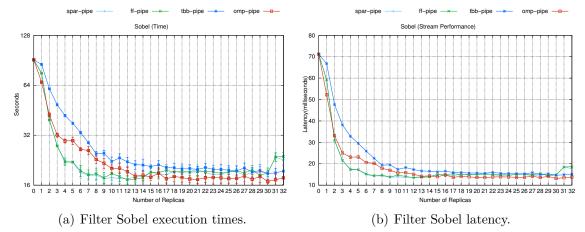

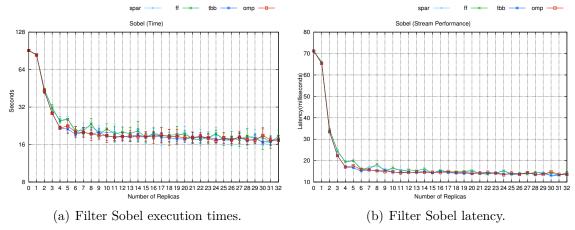

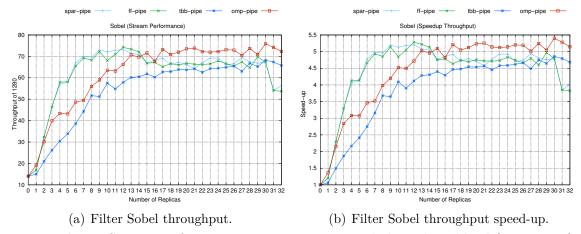

|    |                    | A.1.1  | Filter Sobel SPar Performance         | . 190 |  |

|    |                    | A.1.2  | Filter Sobel Performance Comparison   | . 193 |  |

|    |                    | A.1.3  | Prime Numbers Performance Comparison  | . 198 |  |

|    |                    | A.1.4  | Mandelbrot Set Performance Comparison | . 200 |  |

|    | A.2                | Compl  | lementary Results on Cluster          | . 201 |  |

|    | A.3                | Source | es for Coding Productivity            | . 201 |  |

|    |                    | A.3.1  | Filter Sobel                          | . 202 |  |

|    |                    | A.3.2  | Video OpenCV                          | . 206 |  |

|    |                    | A.3.3  | Mandelbrot                            | . 208 |  |

|    |                    |        | Prime Numbers                         |       |  |

|    |                    | Δ 3 5  | K_Means                               | 213   |  |

# LIST OF FIGURES

| 1 | .1 | Reactive systems representation                                                         | . 8  |

|---|----|-----------------------------------------------------------------------------------------|------|

| 1 | .2 | DataFlow/DataStream systems representation                                              | . 9  |

| 1 | .3 | Stream systems representation                                                           | . 11 |

| 1 | .4 | Thesis flowchart.                                                                       | . 15 |

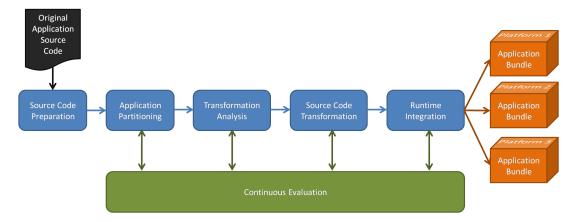

| 2 | .1 | REPARA' workflow. Extracted from [REP16]                                                | . 18 |

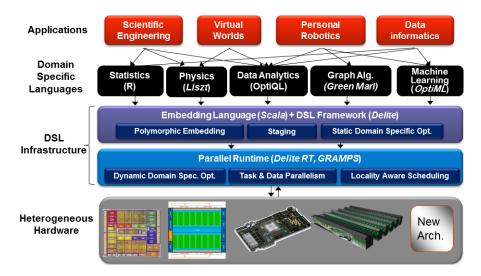

| 2 | .2 | Stanford pervasive parallelism research framework. Extracted from [PPL16]               | . 20 |

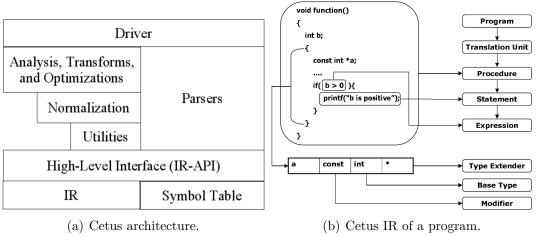

| 2 | .3 | Cetus overview. Extracted from [JLF <sup>+</sup> 05]                                    |      |

|   | .4 | PIPS infrastructure. Extracted from [AAC+11]                                            |      |

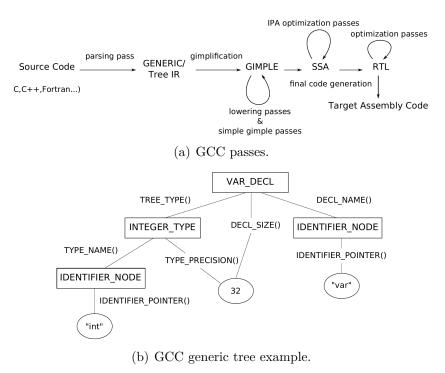

|   | .5 | GCC internals overview. Extracted from [Ló14].                                          |      |

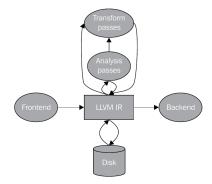

|   | .6 | LLVM infrastructure. Extracted from [LA14]                                              |      |

|   | .7 | ROSE overview. Extracted from [SQ03, ROS16].                                            |      |

| 3 | .1 | The programming framework picture                                                       | . 43 |

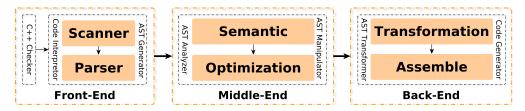

| 3 | .2 | The CINCLE Infrastructure                                                               | . 46 |

| 4 | .1 | The environment of CINCLE infrastructure                                                | . 54 |

| 4 | .2 | CINCLE AST node                                                                         | . 55 |

| 4 | .3 | CINCLE AST representation                                                               | . 56 |

| 4 | .4 | AST visualizations.                                                                     | . 61 |

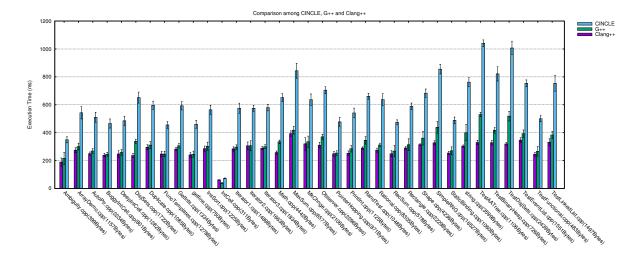

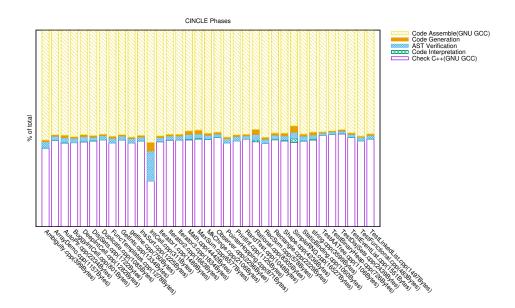

| 4 | .5 | Performance comparison (machine with SSD hard drive)                                    | . 62 |

| 4 | .6 | Only SPar compiler performance (machine with SSD hard drive)                            | . 62 |

|   | .1 | Annotation methodology schema                                                           |      |

|   | .2 | Activity graphs on SPar                                                                 |      |

|   | .3 | SPar Compiler                                                                           |      |

| 5 | .4 | SPar AST                                                                                | . 83 |

| 6 | .1 | Overview of different parallel patterns. Extracted from [MRR12]                         |      |

|   | .2 | A set of task-based parallel patterns for stream parallelism                            |      |

|   | .3 | FastFlow Architecture. Adapted from [DT15]                                              |      |

|   | .4 | FastFlow Queues. Adapted from [Fas16]                                                   |      |

|   | .5 | FastFlow skeletons from the core pattern layer                                          | . 90 |

| 6 | .6 | MPI farm implementation (circle represents process and arrows represent communications) | . 92 |

| 6 | .7 | MPI pipeline implementation (circle represents process and arrows                       |      |

|   |    | represent communications)                                                               | . 93 |

| 6 | .8 | MPI skeleton compositions                                                               | . 93 |

| 6 | .9 | Mapping the transformations to FastFlow generated code                                  | . 99 |

| 6 | 10 | Manning the transformations to MPI generated code                                       | 101  |

xiv List of Figures

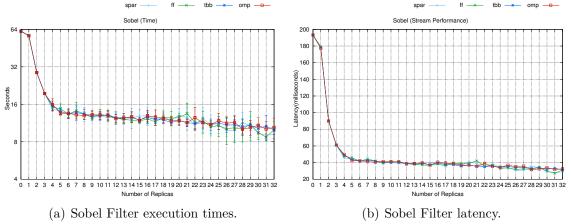

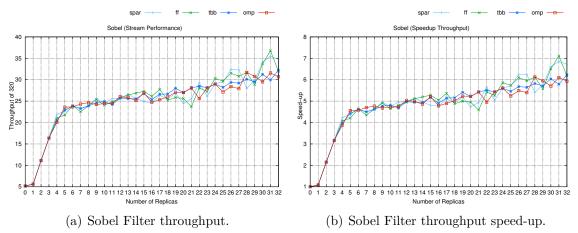

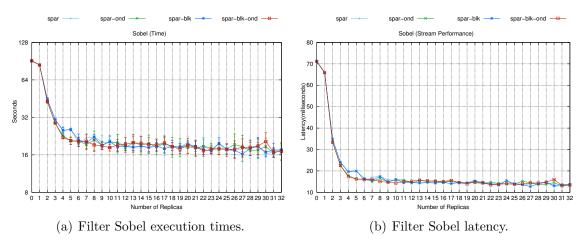

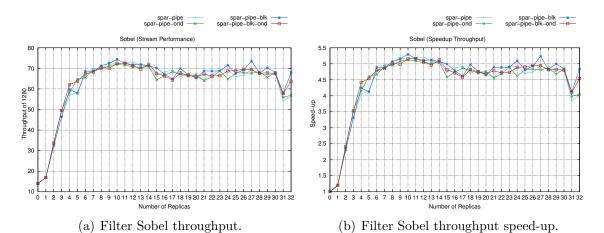

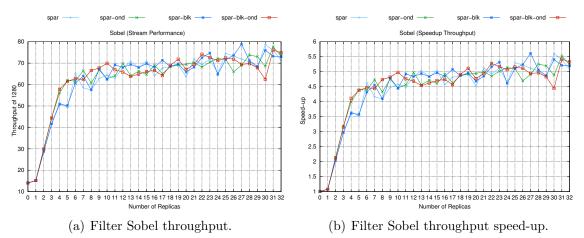

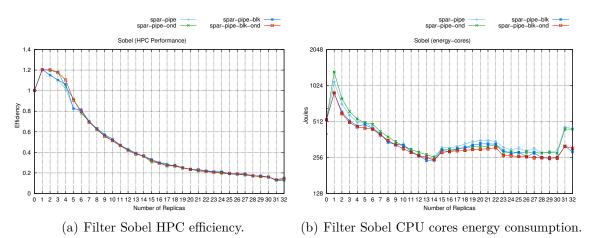

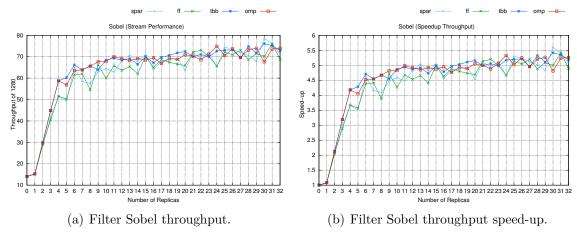

| 7.1  | Time performance using balanced workload (Listing 7.1)                       |

|------|------------------------------------------------------------------------------|

| 7.2  | Time performance using balanced workload (Listing 7.2)                       |

| 7.3  | Stream performance using balanced workload (Listing 7.1) 115                 |

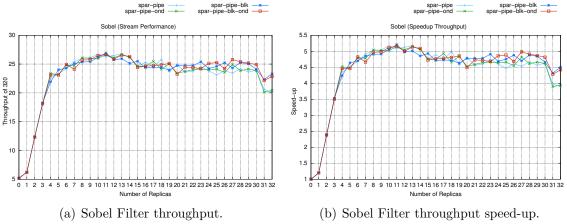

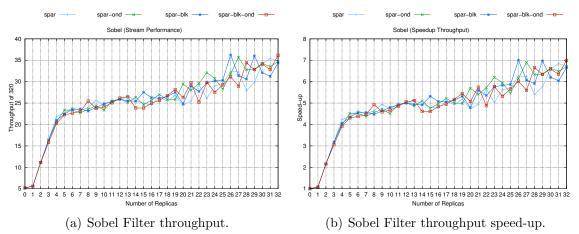

| 7.4  | Stream performance using balanced workload (Listing 7.2) 115                 |

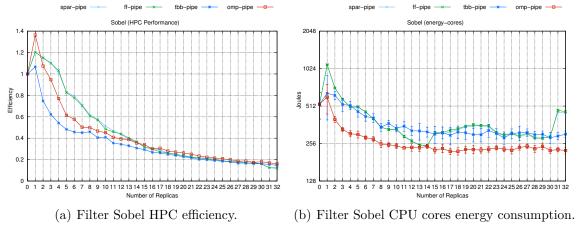

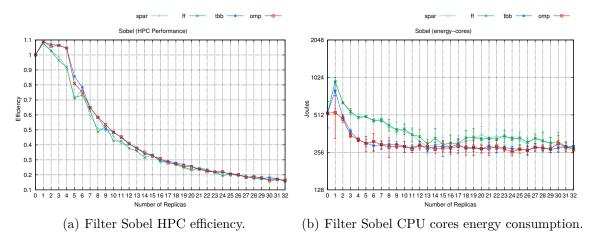

| 7.5  | HPC performance using balanced workload (Listing 7.1) 116                    |

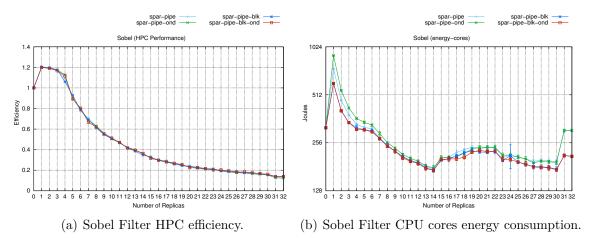

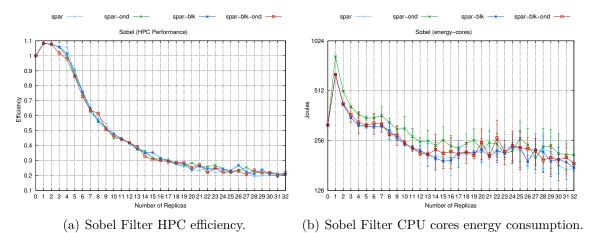

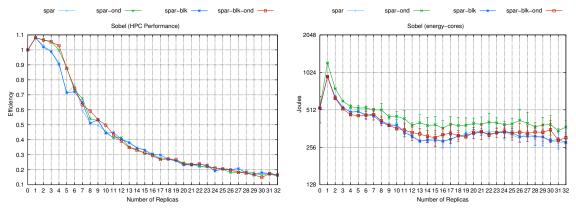

| 7.6  | HPC performance using balanced workload (Listing 7.2) 116                    |

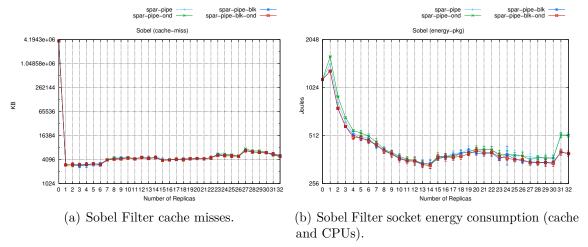

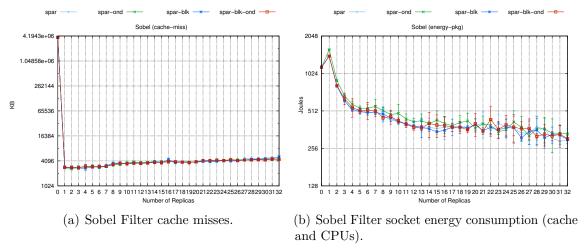

| 7.7  | CPU Socket performance using balanced workload (Listing 7.1) 117             |

| 7.8  | CPU Socket performance using balanced workload (Listing 7.2) 117             |

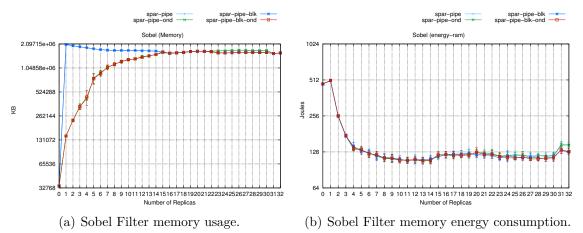

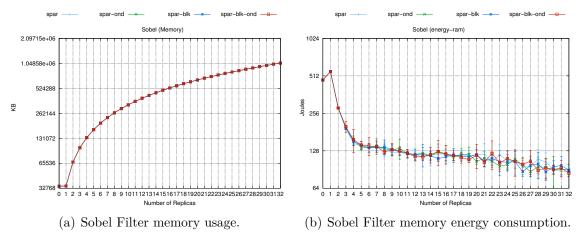

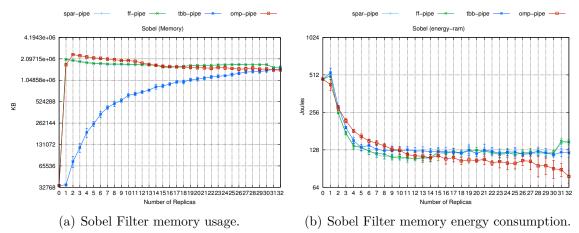

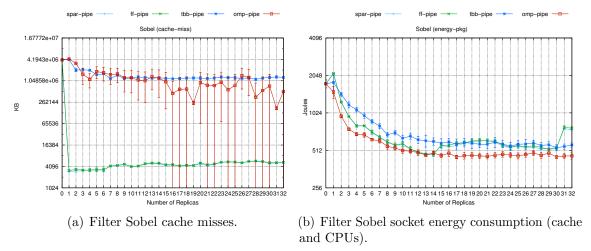

| 7.9  | Memory performance using balanced workload (Listing 7.1) 118                 |

| 7.10 | Memory performance using balanced workload (Listing 7.2) 118                 |

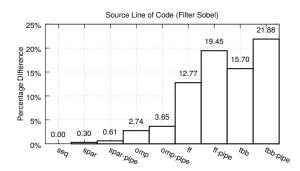

| 7.11 | Source line of code for filter Sobel application                             |

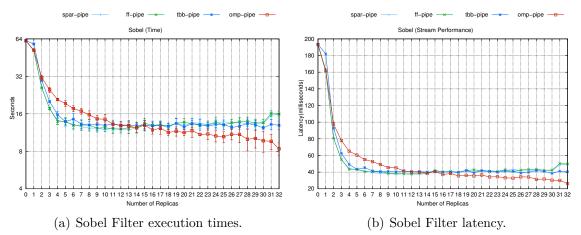

| 7.12 | Time performance comparison using balanced workload (Listing $7.1$ ) . $121$ |

| 7.13 | Time performance comparison using balanced workload (Listing 7.2) . 121      |

| 7.14 | Stream performance comparison using balanced workload (Listing 7.1) 121      |

| 7.15 | Stream performance comparison using balanced workload (Listing 7.2) 122      |

| 7.16 | HPC performance comparison using balanced workload (Listing 7.1) . 122       |

| 7.17 | HPC performance comparison using balanced workload (Listing 7.2) . 123       |

| 7.18 | CPU Socket performance comparison using balanced workload (Listing           |

|      | 7.1)                                                                         |

| 7.19 | CPU Socket performance comparison using balanced workload (Listing           |

|      | 7.2)                                                                         |

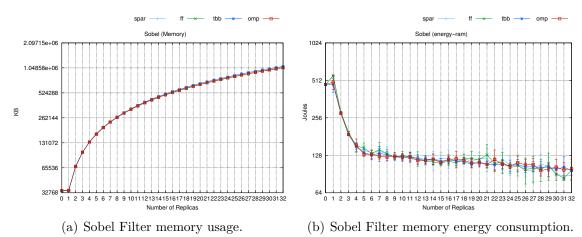

| 7.20 | Memory performance comparison using balanced workload (Listing $7.1$ ) $124$ |

| 7.21 | Memory performance comparison using balanced workload (Listing 7.2) 125      |

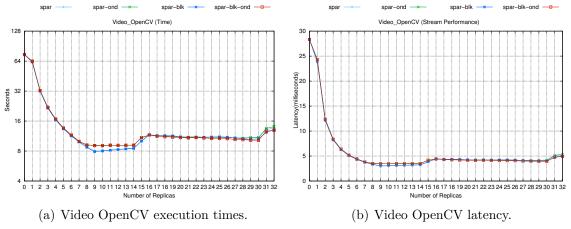

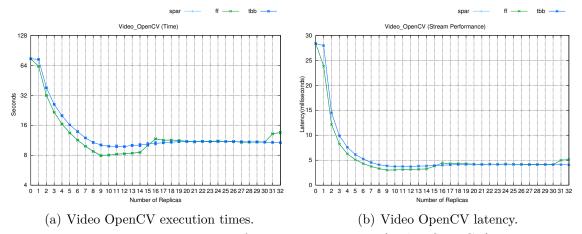

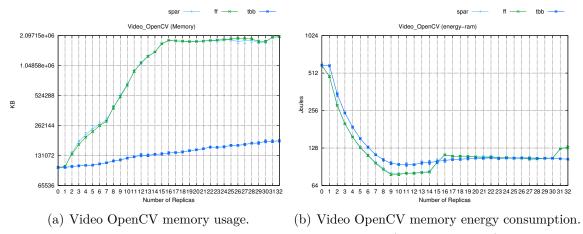

| 7.22 | Time performance (Video OpenCV)                                              |

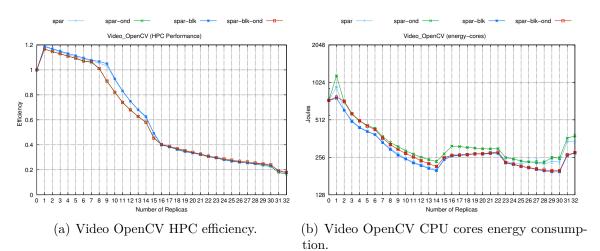

| 7.23 | Stream performance (Video OpenCV)                                            |

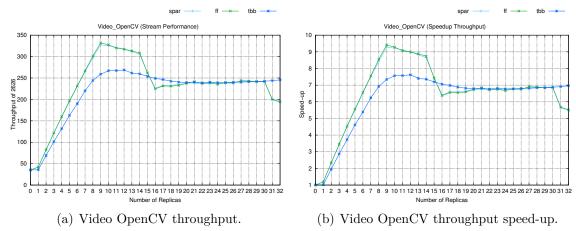

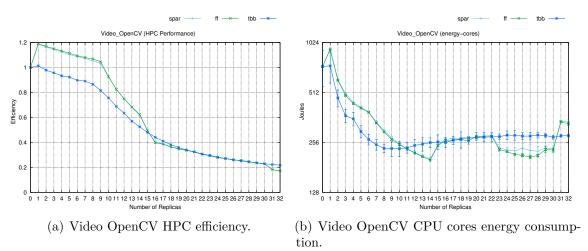

| 7.24 | HPC performance (Video OpenCV)                                               |

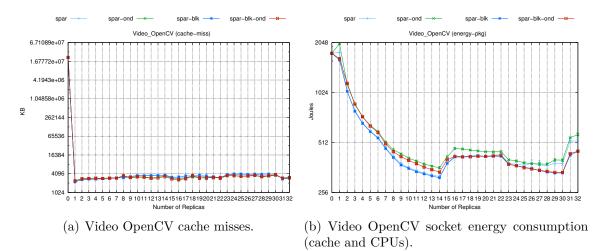

| 7.25 | CPU Socket performance (Video OpenCV)                                        |

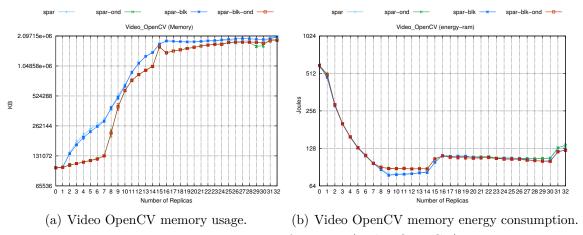

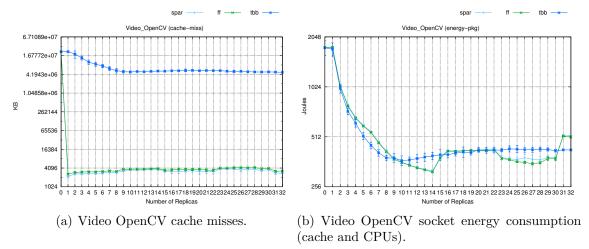

| 7.26 | Memory performance (Video OpenCV)                                            |

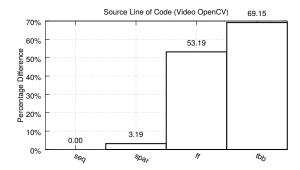

|      | Source line of code for Video OpenCV application                             |

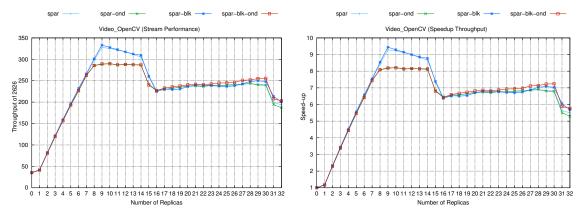

| 7.28 | Time performance comparison (Video OpenCV)                                   |

| 7.29 | Stream performance comparison (Video OpenCV)                                 |

| 7.30 | HPC performance comparison (Video OpenCV)                                    |

| 7.31 | CPU Socket performance comparison (Video OpenCV)                             |

| 7.32 | Memory performance comparison (Video OpenCV)                                 |

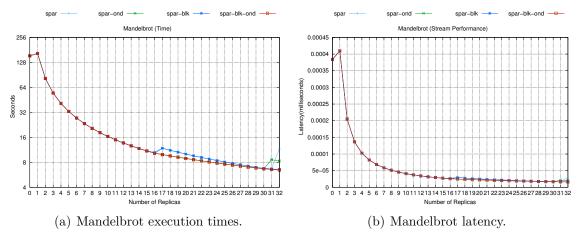

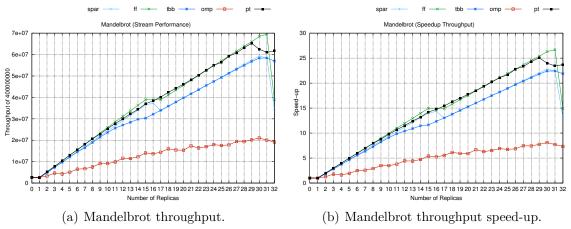

| 7.33 | Time performance (Mandelbrot)                                                |

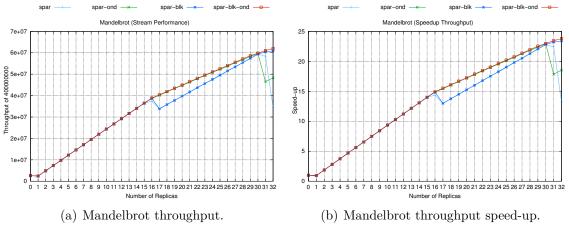

| 7.34 | Stream performance (Mandelbrot)                                              |

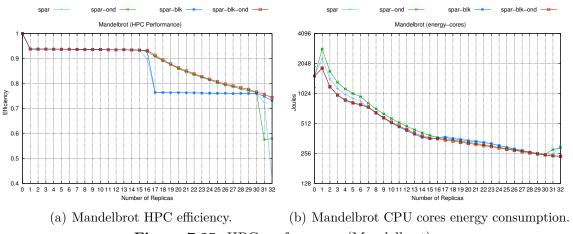

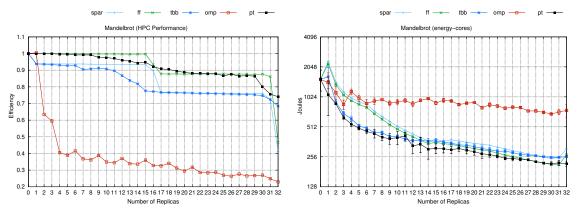

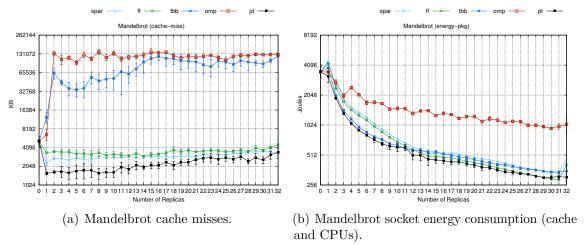

| 7.35 | HPC performance (Mandelbrot)                                                 |

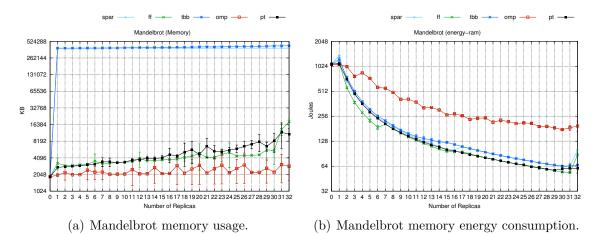

| 7.36 | CPU Socket performance (Mandelbrot)                                          |

| 7.37 | Memory performance (Mandelbrot)                                              |

| 7.38 | Source line of code for Mandelbrot application                               |

| 7.39 | Time performance comparison (Mandelbrot)                                     |

| 7.40 | Stream performance comparison (Mandelbrot)                                   |

List of Figures xv

| 7.41 | HPC performance comparison (Mandelbrot)                                                                                                              |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7.42 | CPU Socket performance comparison (Mandelbrot)                                                                                                       |

| 7.43 | Memory performance comparison (Mandelbrot)                                                                                                           |

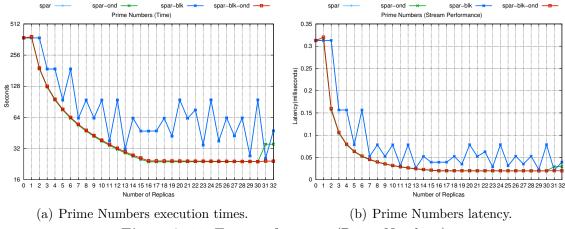

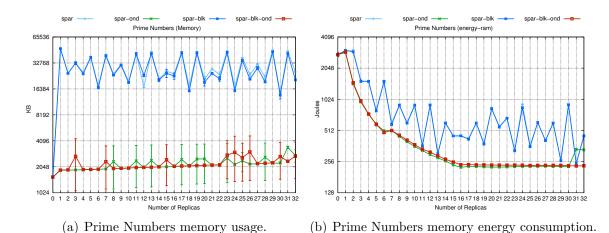

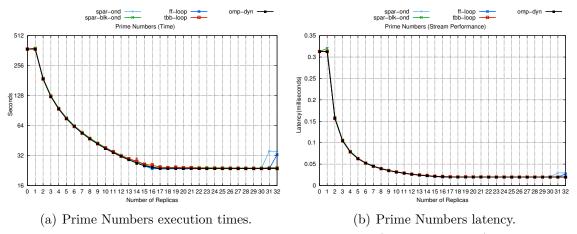

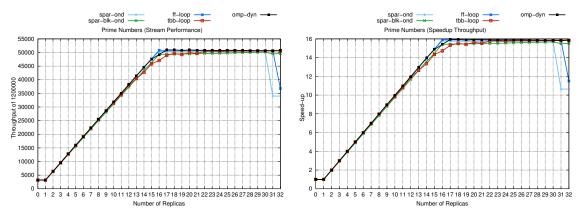

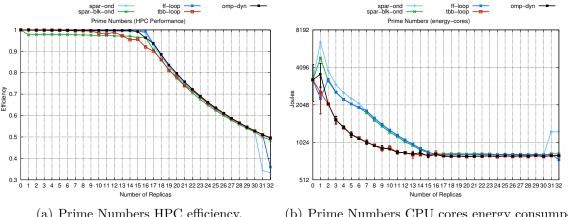

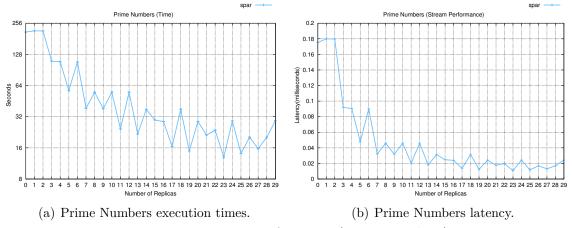

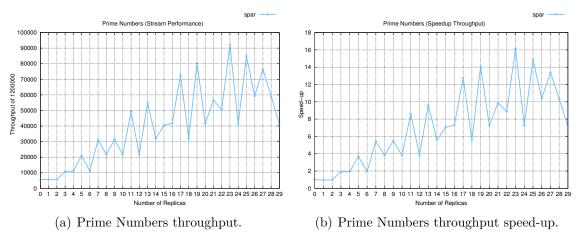

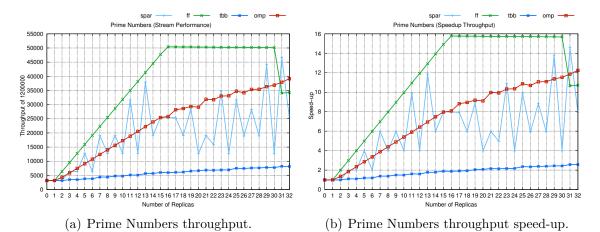

| 7.44 | Time performance (Prime Numbers) $\dots \dots \dots$ |

| 7.45 | Stream performance (Prime Numbers)                                                                                                                   |

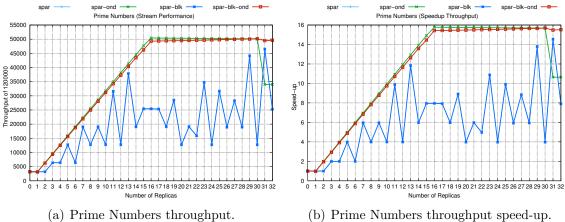

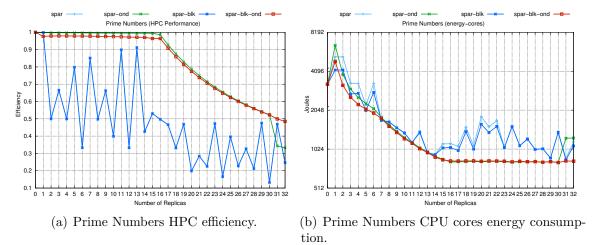

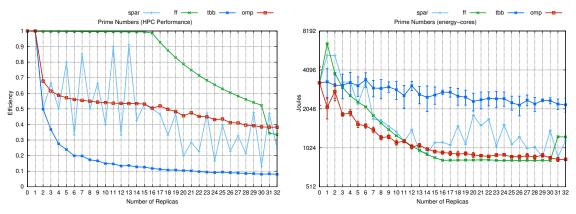

|      | HPC performance (Prime Numbers)                                                                                                                      |

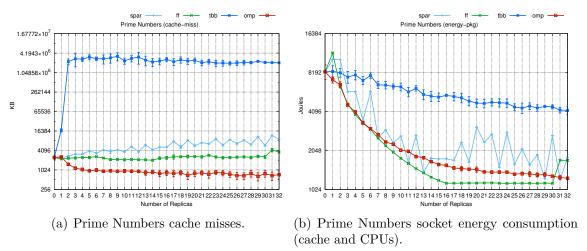

|      | CPU Socket performance (Prime Numbers)                                                                                                               |

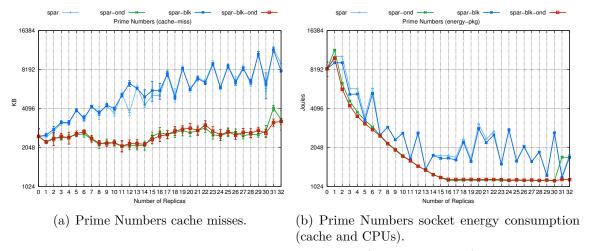

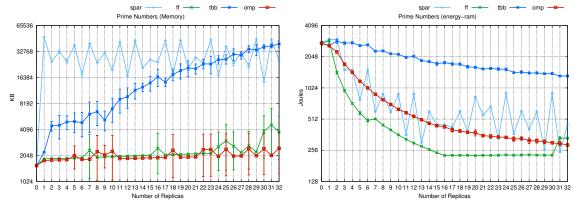

| 7.48 | Memory performance (Prime Numbers)                                                                                                                   |

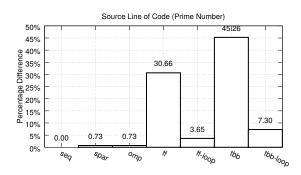

|      | Source line of code for Prime Number application                                                                                                     |

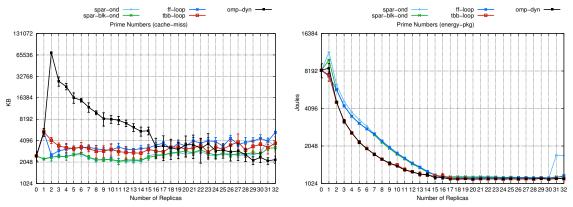

| 7.50 | Time performance comparison (Prime Numbers) $\dots \dots 145$                                                                                        |

|      | Stream performance comparison (Prime Numbers)                                                                                                        |

|      | HPC performance comparison (Prime Numbers)                                                                                                           |

| 7.53 | CPU Socket performance comparison (Prime Numbers)146                                                                                                 |

| 7.54 | Memory performance comparison (Prime Numbers)                                                                                                        |

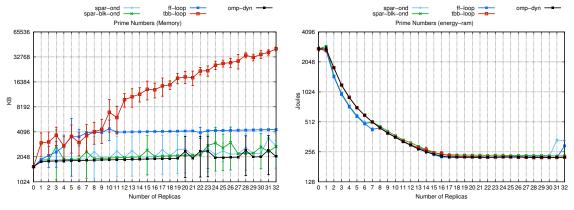

|      | Time performance (K-Means)                                                                                                                           |

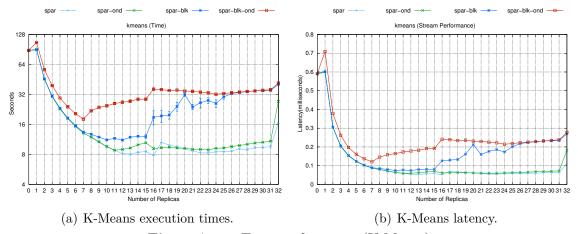

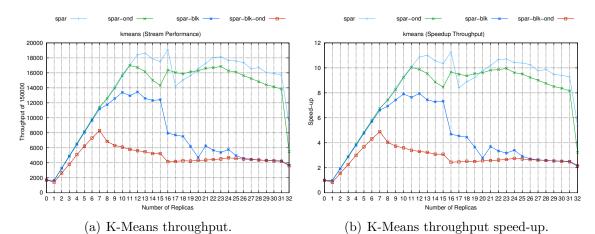

|      | Stream performance (K-Means)                                                                                                                         |

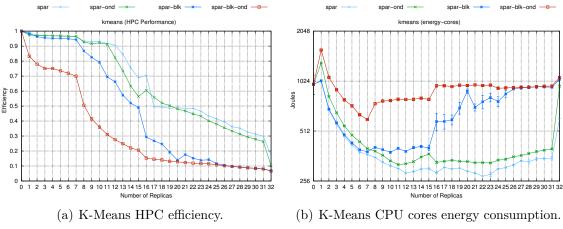

| 7.57 | HPC performance (K-Means)                                                                                                                            |

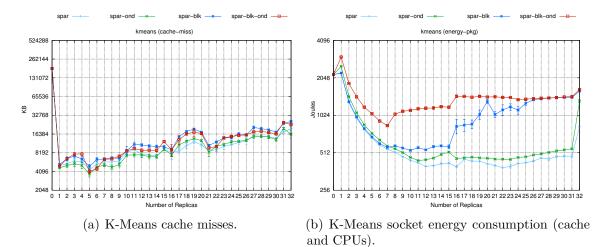

| 7.58 | CPU Socket performance (K-Means)                                                                                                                     |

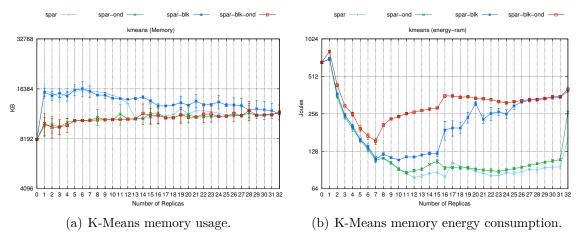

| 7.59 | Memory performance (K-Means)                                                                                                                         |

| 7.60 | Source line of code for K-Means application                                                                                                          |

| 7.61 | Time performance comparison (K-Means)                                                                                                                |

|      | Stream performance comparison (K-Means)                                                                                                              |

| 7.63 | HPC performance comparison (K-Means)                                                                                                                 |

| 7.64 | CPU Socket performance comparison (K-Means)                                                                                                          |

|      | Memory performance comparison (K-Means)                                                                                                              |

| 7.66 | Time performance using balanced workload (Sobel Filter)                                                                                              |

|      | Stream performance using balanced workload (Sobel Filter) 157                                                                                        |

| 7.68 | Time performance (Prime Numbers) $\dots \dots \dots$ |

| 7.69 | Stream performance (Prime Numbers)                                                                                                                   |

| 9.1  | Statistics of Stream<br>It benchmarks [TA10]. Extracted from [Won12] $171$                                                                           |

| A.1  | Time performance using unbalanced workload (pipe-like) 190                                                                                           |

| A.2  | Time performance using unbalanced workload (farm-like) 190                                                                                           |

| A.3  | Stream performance using unbalanced workload (pipe-like) 191                                                                                         |

| A.4  | Stream performance using unbalanced workload (farm-like) $\dots \dots 191$                                                                           |

| A.5  | HPC performance using unbalanced workload (pipe-like) 191                                                                                            |

| A.6  | HPC performance using unbalanced workload (farm-like) 192                                                                                            |

| A.7  | CPU Socket performance using unbalanced workload (pipe-like) $\ \ldots \ 192$                                                                        |

| A.8  | CPU Socket performance using unbalanced workload (farm-like) $192$                                                                                   |

| A.9  | Memory performance using unbalanced workload (pipe-like) $$ 193                                                                                      |

| A.10 | Memory performance using unbalanced workload (farm-like) 193                                                                                         |

| A.11 | Time performance comparison using unbalanced workload (Listing $7.1$ ) $194$                                                                         |

|      |                                                                                                                                                      |

xvi List of Figures

| A.12 Time performance comparison using unbalanced workload (Listing 7.2) 194                                                 |

|------------------------------------------------------------------------------------------------------------------------------|

| A.13 Stream performance comparison using unbalanced workload (Listing $7.1$ ) 194                                            |

| A.14 Stream performance comparison using unbalanced workload (Listing 7.2) 195                                               |

| $A.15~\mathrm{HPC}$ performance comparison using unbalanced workload (Listing 7.1) 195                                       |

| A.16 HPC performance comparison using unbalanced workload (Listing 7.2) 195                                                  |

| A.17 CPU Socket performance comparison using unbalanced workload (List-                                                      |

| $ing 7.1) \dots \dots$ |

| A.18 CPU Socket performance comparison using unbalanced workload (List-                                                      |

| $ing 7.2) \dots \dots$ |

| A.19 Memory performance comparison using unbalanced workload (Listing                                                        |

| 7.1)                                                                                                                         |

| A.20 Memory performance comparison using unbalanced workload (Listing                                                        |

| $7.2)  \dots  \dots  \dots  197$                                                                                             |

| A.21 Time performance comparison (Prime Numbers Default) 198                                                                 |

| A.22 Stream performance comparison (Prime Numbers Default) 198                                                               |

| A.23 HPC performance comparison (Prime Numbers Default) 199                                                                  |

| A.24 CPU Socket performance comparison (Prime Numbers Default) $\dots$ 199                                                   |

| A.25 Memory performance comparison (Prime Numbers Default) 199                                                               |

| A.26 Stream performance comparison (Mandelbrot) 200                                                                          |

| A.27 Time performance using unbalanced workload (Filter Sobel) $\dots \dots 201$                                             |

| A.28 Stream performance using unbalanced workload (Filter Sobel) 201                                                         |

# LIST OF TABLES

| 2.1<br>2.2 | Related works for C/C++ DSL design space         |

|------------|--------------------------------------------------|

|            | Basic API functions                              |

| 5.1        | Statistics of SPar annotations on the experiment |

|            | The Pianosau machine configurations              |

# Part I

Scenario

# 1

## Introduction

$This\ chapter\ will\ introduce\ and\ contextualize\ the\ dissertation\ research.$

#### Contents

| 1.1 Co | entextualization                       |

|--------|----------------------------------------|

| 1.1.1  | Perspectives on High-Level Parallelism |

| 1.1.2  | 2 Stream Parallelism Domain            |

| 1.2 Go | pals                                   |

| 1.3 Co | ontributions                           |

| 1.4 Ou | tline                                  |

4 1. Introduction

#### 1.1 Contextualization

In order to contextualize the research problems and challenges, the first section will present the central perspectives regarding high-level parallelism. The goal is to present the main challenges and issues of providing high-level parallelism in respect to the state-of-the-art alternatives, and show how our research provides solutions to these concerns. The subsequent section will introduce the stream parallelism domain and highlight its central difficulties when parallelizing with current state-of-the-art tools. Additionally, we believe that stream parallelism properties are generic enough to increase the level of abstraction. Thus, we will show their advantages and how we plan to implement them using a standard C++ mechanism.

#### 1.1.1 Perspectives on High-Level Parallelism

For many years parallel computing has been mostly considered in specialized super-computer centers, but this has dramatically changed in the last decade. Currently, there are different degrees of parallelism from embedded systems to high-performance servers, due to the availability of multiprocessing architectures such as multi-core, accelerators and clusters [RJ15, RR10]. Also, technology improvements have contributed to increasing the capabilities of hardware resources such as memory, network and storage, and supporting complex software on different kinds of devices. This heterogeneity raises many challenges for software developers regarding performance portability<sup>i</sup>, code portability<sup>ii</sup> and coding productivity<sup>iii</sup>.

In the software industry, many general-purpose programming languages are making progress on higher-level abstractions, supporting software engineers in the building process of complex applications with better code productivity. However, these applications have many challenges to achieve performance and code portability on parallel architectures while preserving their coding productivity. Unfortunately, compilers such as GCC are not able to automatically parallelize code from these high-level language abstractions. In fact, from a compiler's point of view only vectorized code is automatically parallelized, while other high-level abstractions (viewed as coarse-grained code regions) do not provide the necessary semantic information for the compiler to perform code parallelization. Consequently, developers are forced to restructure their application by using low-level and architecture-dependent programming interfaces

<sup>&</sup>lt;sup>i</sup>It means the code achieves the same performance on different platforms and architectures.

<sup>&</sup>lt;sup>ii</sup>Allows a code to run in different architectures and platforms without any changes.

iii Reduces the amount of code and programming effort.

such as MPI [GHLL<sup>+</sup>98], CUDA [KmWH10] and Pthreads [NBF96] if they hope to exploit parallel hardware efficiently.

The current software development process consists of prototyping an efficient program in a high-level language and then implementing some kind of high-performance code. This two-step process is very time-consuming, especially if we take into account that the code eventually produced is strongly architecture-dependent. For instance, it requires the programmer to have expert knowledge in hardware and parallel programming to produce high-performance code when targeting different architectures. In big team projects, some programmers will work on the high-level part while others will have to implement the lowest-level version of the application. The problem is that different versions of the parallelized application will have to be implemented in order to target different architectures. Thus, a project will usually have many versions that differ slightly from the original and any update could require rethinking the parallelization strategy in order to better exploit the architecture's resources.

To solve this problem, the Domain-Specific Language (DSL) approach has proven to be a suitable alternative to high-level parallelism abstractions in recent years [Gri12, GAF14, GF13, AGLF15a, AGLF15b]. Also, DSLs have proven to be effective when targeting code productivity, code portability, and performance in different general-purpose programming languages [SLB+11, DJP+11, HSWO14, Suj14]. Though these solutions lack generality, they increase optimization and abstraction to enable the user to focus on better ideas and algorithms rather than on general problems related to parallelism exploitation.

A DSL can be implemented using different techniques. An "External" DSL implementation is a language completely distinct from the host language. Thus, it is necessary to create a custom compiler [Fow10, Gho11]. Usually, external DSLs are more flexible and easier to model for the domain-specific scenario. Yet, depending on the environment, they require much more expertise in compiler design even using compiler frameworks like LLVM, because the high-level interface must be translated into the low-level intermediate representation. On the other hand, "Internal" DSL implementations are fully integrated with the host language syntax and semantics. They are provided as a library or by using specific host language mechanisms [VBD+13]. Our DSL uses the embedded C++11 attributes [ISO11b, ISO14] already present in the host language grammar and therefore it is "de facto" an internal/embedded DSL.

According to the literature, an internal DSL should be easier to implement because the host language should provide an alternative to suitably integrate custom language constructions. However, in C++, the context is entirely different when one intends to use its standard annotation mechanism. It requires a profound knowledge of compiler design. We solved this problem by providing a new compiler infrastructure so that we can provide a suitable alternative because the literature does not enable higher abstraction level and aggressive code transformations. In addition, our programming

6 1. Introduction

framework perspective aims to facilitate other kinds of language extensions or compiler-based tools to benefit from the infrastructure. This and other new perspectives will be discussed and proven throughout this dissertation.

In spite of the DSL benefits, designing an embedded C++ DSL for high-level parallelism abstractions is still a challenging task. It requires expertise in multiple areas such as parallel programming, programming languages, compiler architecture, etc. Recently, researchers from Stanford University have been working on the same subject to create high-performance and high-level embedded DSLs for the Scala language [OSV10]. They developed the Delite compiler framework to enable DSL designers to quickly and efficiently target parallel heterogeneous hardware [SBL<sup>+</sup>14]. Overall, their research builds on a stack of domain-specific solutions that in principle share similar goals with this work. In contrast, our idea is to contribute to the C/C++ [Str14] community, which is widely used in several market and real world applications.

Delite is logically between a high-level application DSL and low-level hardware and runtime libraries. Integrated with Scala, its framework provides parallel patterns that can be instantiated by the application's DSL designer without worrying about the parallelism aspect of heterogeneous hardware. Unlike C++, Scala is more recent and was created along with the DSL support implementation, which requires parallelism abstractions. In our proposed research, in addition to providing high-level parallelism to an application's DSL designers, we have also proposed a compiler infrastructure as an alternative for experts in parallelism exploitation to quickly prototype DSLs based on annotations. This contribution can significantly improve the abstraction level of parallelism in C++ programs. Similar to Delite, we propose an embedded C++ domain-specific language, yet for stream-oriented parallelism. Our goal is that the programmer will not be required to instantiate patterns or methods as in Delite. Instead we aim to preserve the application's source code as much as possible, only requiring the programmer to insert proper annotations for annotating the stream parallelism features.

In the C++ community, a research closest to ours is Re-engineering and Enabling Performance and poweR of Applications (REPARA) [REP16]. Its vision is to help develop new solutions for parallel heterogeneous computing [GSFS15] in order to strike balance between source code maintainability, energy efficiency, and performance [DTK15]. In general, REPARA differs from our work in many ways, but shares the idea of maintaining the source code by introducing abstract representations of parallelism through annotations [DGS+16]. Thus, a standard C++11 attribute mechanism is used as skeleton-like code annotations (farm, pipe, map, for, reduce, among others). Attributes are preprocessed and exploited within a methodology, which eventually produces code targeting heterogeneous architectures.

From the high-level parallelism perspective of REPARA, attributes are interpreted by a refactoring tool that is on top of eclipse IDE (Integrated Develop-

ment Environment), which is responsible for the source-to-source transformations to C++/FastFlow. As a consequence of refactoring methodologies, these transformations occur in place and produce code that is transparent to users. Like REPARA, we aim to be standard C++ compliant. However, in our programming framework, attributes are used at compiler level and source-to-source code transformations are hidden from the users. Moreover, our goal is to be domain-specific for stream parallelism, targeting multi-core and clusters to support an application's DSL designer as in the Delite framework's vision.

There are also other programming interfaces that provide high-level parallelism that are not DSLs. Examples are MapReduce [MS12, DG08, CCA<sup>+</sup>10, Had16], Charm++ [AGJ<sup>+</sup>14, Cha16], X10 [Mil15, X1016], Spark [KKWZ15], Storm [And13], and Intel Cilk Plus [BJK<sup>+</sup>95, Cil16]. While offering many suitable features for different applications, these approaches force programmers to deal with different programming models that are not natural to the application domain. This negatively impacts coding productivity. Moreover, it is difficult for them to provide good performance when targeting different parallel architectures, because their embedded interface is still too low-level. Therefore, they require different implementation versions of the source code to target different hardware.

Our perspective on high-level parallel programming relies on language attributes that annotate abstract representations of potential parallelism. In our vision, other annotation-based models such as OpenMP [Qui03] are conceptually much lower-level, because users have to express the parallelism and deal with low-level details relative to high-performance coding. These interfaces achieve coding productivity only in specific cases such as independent loop parallelization. In addition, code portability is still strongly architecture-dependent, which requires the production of different versions of the application in order to target other architectures.

# 1.1.2 Stream Parallelism Domain

Stream processing is one of the most commonly used paradigms in computer systems [TA10, AGT14]. We can find it in our daily software applications and computational hardware. All personal computer processors run a sequence of instructions in a streaming fashion to achieve throughput, latency, and quality of service at the user level. On the software side, the increase of the Internet of Things (IoT) field and the big data explosion has made stream processing a trending topic in computer science. There are millions of data sources on the Internet that are collecting and exchanging information through devices and social media. Therefore, the need for high throughput and low latency is also crucial for software that deals with image, video, networking, and real time data analysis.

1. Introduction

Different variants of the stream programming paradigm have emerged over the years (reactive, DataFlow and stream parallelism) [TA10, AGT14, TKA02a, ADKT14, ADK+11]. They characterize the stream as a set of continuous data/instructions/tasks that flows naturally through a sequence of operations. Each operation consumes input and produces output like an assembly line that is also called as a pipeline. In general, stream processing has a continuous flow and unbounded stream behavior. However, some of today's application scenarios are irregular and have bounded streams. Consequently, it is a challenge for stream-based systems to control the end of the stream and maintain good performance even if there is not infinite flow.

Stream processing variants share similar motivations, goals, and characteristics that make it difficult for a layperson to differentiate among them. Some scientists simply say that they are equivalent in many aspects. In fact, they all share the same principles. However, the resulting systems have subtle distinctions. It is possible to highlight that, for example, a reactive system is more concerned with latency than throughput. A typical example is a spreadsheet, where a person is usually applying several mathematical equations (stream operations) in the data cells (stream sources). Subsequently, the system reacts to all data updated in the cell, ensuring that latency is small when compared to human perception [Fur14].

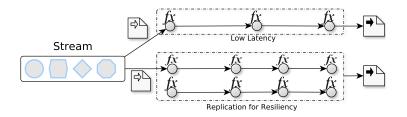

A representation of reactive environmental characteristics can be found in Figure 1.1. Each actor in the system propagates operation results and reacts when they receives a new input event. Many web services use reactive programming for different types of events. For instance, the most common is to answer over click events such as subscriptions to a social network and to purchase goods. The system may have to deal with different click sources and instantaneously react to the event. Thus, parallelism is especially designed for each application to achieve latency, attend many events, react over data scaling, and recover when failures happen in a timely manner.

Figure 1.1: Reactive systems representation.

Listing 1.1 illustrates an example of a simple reactive stream code from the programming perspective. It is a program that reads events from the keyboard and can print the multiplication table. Therefore, the stream source is a digit or a set of digits that will be processed to return a multiplication table. Through this example it is possible to see the following challenges: Providing scalability and low response time when the user enters a set of digits to be computed; and preserving resiliency when

a non-digit character is inserted so that the application does not stop, crash or lose information.

Listing 1.1: Reactive stream code example.

DataFlow programming is another stream-based paradigm, which is also called DataStream by some scientists to avoid being confused with the architectural term DataFlow [AGT14]. It is a way for runtime systems to automatically extract parallelism from an application. In order to do so, the programmer explicitly indicates how data will flow in the program in such a way that the system may build a Directed Acyclic Graph (DAG). Then, when there are independent operations, that have all of their input data available, they are designed to execute in parallel.

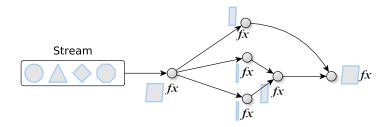

Figure 1.2: DataFlow/DataStream systems representation.

A representative illustration can be found in Figure 1.2, where the spheres are operators and arrows are dependencies. Usually, DataFlow computations are represented through dependency graphs in the main memory. Operators are processed by threads or processes as soon as all their input data items become available as shown in Figure 1.2. Hence, each data operator thread will know when its work can be done and go ahead. When input dependencies are used it means that an operator can only perform its computation after the input data is available. Similarly, an output dependency is a specification for subsequent operators stating where they will obtain their results. Consequently, the connections and synchronizations between operators are represented and ensured by input and output dependencies. This behavior is quite similar to reactive programming. However, DataFlow is more closely related to data parallelism than event driven parallelism (reactive systems).

1. Introduction

When looking at the literature regarding parallel programming interfaces for multi-core architectures, we can point out different solutions that target the DataFlow paradigm [CJvdP07, PC11, Omp16]. OpenMP was originally designed for data parallelism in FORTRAN and C, but has also introduced task parallelism and some clauses (depend, in, out, inout) targeting a kind of DataFlow parallelism in task regions since its 4.0 version. A simple code example is given in Listing 1.2 to illustrate the programmer's point of view, presenting a program that performs a sequence of operations over a contiguous bounded data stream.

```

void proc(){

#pragma omp parallel

#pragma omp single

for (int i = 0; i < NREGION; ++i)

int *persons = new int [NPERSON];

//task group 1

#pragma omp task depend(out: persons[i])

8

load (persons);

#pragma omp task depend(in: persons[i])

//task group 2

13

regions_min[i] = min(persons);

14

#pragma omp task depend(in: persons[i])

//task group 3

regions_max[i] = max(persons);

18

19

20

23

}

```

Listing 1.2: OpenMP DataFlow code example.

The program performs a data analysis to identify the maximum and minimum age of people in each region. Therefore, the loop iterates for each region, loading everyone's age into a vector to find and store the maximum and minimum age. In order for OpenMP to exploit DataFlow parallelism, we have to describe the data dependencies in such a way that OpenMP can run the max and min operations in parallel, as presented in Listing 1.2 in the pragma task annotations. Nonetheless, its usage is strongly dependent on the OpenMP programming model. For instance, it is not enough to describe the data dependency. One must be aware of task parallelism, where task pragmas are a group of tasks that will run concurrently, and the output and input dependency will synchronize the data flow. In our OpenMP example, the first task group will update the input data of the next two task groups (max and min operators) so that they execute in parallel. Finally, note that a DataFlow region must also be encapsulated by parallel and single directives.

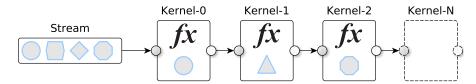

Stream parallelism programming inherits many of the capabilities of previous paradigms. In contrast to DataFlow programming, stream operations' dependencies are not determined by input and output data specifications. In stream parallelism, the operation sequence is structured in such a way that dependencies are evidenced and input and output describes what will be consumed and produced by a kernel as illustrated in Figure 1.3. A kernel is composed of an operator or a set of operations performed at each element of the stream.

Inside kernels, operations are expected to be sequential and they are performed locally during the computation. The specifications of input and output also help the system to prevent global data manipulation, whereas local operations can improve memory performance through data locality. The stream parallelism paradigm also simplifies the implementation of the task scheduler since the flow is completely deterministic. In DataFlow for example, the model is highly data dependent, resulting in a non-deterministic flow and complex scheduler implementation because the flow of tokens within the graph may vary depending on the input token values during the execution of the program. Depending on the token flow, the scheduler should make different scheduling decisions.

Figure 1.3: Stream systems representation.

Stream parallelism applications work over intensive and unbounded streams, focusing on high throughput rates and low latency. The undefined end of a stream is a difficult for DataFlow systems. On the other hand, stream systems have DataFlow semantics. Therefore, not all the graphs we can express with DataFlow may be expressed with stream parallelism. For example, similar undefined behavior is also present in reactive applications, but there is an elastic stream (a set of events) frequency that must be addressed in timely manner, while stream applications usually have bigger streams with a constant frequency where the throughput may be a priority instead of latency. Examples of real world applications are face tracking, video streaming, network packet routing, image processing, among others. Listing 1.3 outlines the structure of a typical stream parallel application.

The code example implements a stream application, where each element of the stream is a string. Therefore, the stream application starts on the "while" loop. At each iteration, the loop reads a stream element, computes a result using the element, and writes the result on a given output stream. The end of the stream is monitored by a condition checked after reading one element. Note that it is common that the number of computations of the stream elements (also called as filter) vary among the

1. Introduction

applications, but a stream application will usually have a sequence for these three operations: read, filter, and write [TA10].

```

void proc_seq() {

std::string stream_element;

while(1) {

read_in(stream_element); //reads each element of a given stream

if(stream_in.eof()) break; //test if stream is empty

compute(stream_element); //apply some computation to the stream

write_out(stream_element); //write the results into a given output

stream

}

```

**Listing 1.3:** Stream application code example.

Due to the fact that OpenMP is not designed for naturally annotating these kinds of applications, the most efficient way to explore stream parallelism is to use FastFlow [Fas16, ADKT14] or TBB [Rei07, TBB16] frameworks. Both frameworks also support DataFlow parallelism and present a similar programming interface because they leverage the same meta-programming features. However, the runtime systems are very different as are the design goals, which will be explained in detail later in this dissertation (Chapter 2). To exemplify the expressiveness of stream parallelism when using such frameworks, a pseudo code in FastFlow is given in Listing 1.4, extending the example of Listing 1.3. From this code, we can point out the main drawbacks of these frameworks are source code rewriting and restructuring.

```

struct firstStage: ff_node_t<std::string> {

std::string stream_element;

std::string *svc(std::string *) {

while (1) {

read_in(stream_element);

if (stream_in.eof()) break;

ff_send_out(new std::string(stream_element));

return EOS;

};

11

struct secondStage: ff_node_t<std::string> {

std::string *svc(std::string *stream element) {

13

compute(*stream_element);

14

return stream_element;

15

17

struct thirdStage: ff_node_t<std::string> {

std::string *svc(std::string *stream_element) {

19

write_out(*stream_element);

20

delete stream_element;

return GO ON;

23

}

```

1.2. Goals 13

**Listing 1.4:** FastFlow stream code example.

In contrast to these frameworks, the scope of this research is limited to stream parallelism and does not address similar approaches such as DataFlow or Reactive parallelization. The main expected state-of-the-art contribution is to provide a high-level DSL for expressing stream parallelism. Even though C++ template libraries can provide interesting coding productivity and abstractions, this work aims to raise the abstraction level without significantly affecting performance. The proposal is to use the standard C++ attribute mechanism [MW08, ISO14], maintaining on-the-fly stream parallelism such as the example in Listing 1.5, where the sequential source code (Listing 1.3) is not restructured. Chapter 5 will present and discuss the proposed DSL in detail to address stream parallelism by using standard C++ attributes.

```

void proc_spar() {

std::string stream_element;

[[spar::ToStream, spar::Input(stream_element)]]    while(1) {

read_in(stream_element);

if(stream_in.eof()) break;

[[spar::Stage, spar::Input(stream_element), spar::Output(stream_element)]]

{ compute(stream_element); }

[[spar::Stage, spar::Input(stream_element)]]

{ write_out(stream_element); }

}

```

**Listing 1.5:** Proposal interface exemplification for stream parallelism.

# 1.2 Goals

The main objectives of this dissertation are the following:

- G1: The first goal is to provide support tools that enable parallel programming experts to create standard C++ embedded DSLs.

- **G2**: The second goal is to provide high-level stream parallelism and coding productivity without significant performance degradation in multi-core systems.

1. Introduction

• **G3**: The third goal is to introduce code portability in multi-core and cluster systems.

# 1.3 Contributions

This work contributes to a programming framework for high-level parallelism abstractions that includes the following specific contributions:

- C1: A compiler infrastructure for generating new language extensions in C/C++.

- C2: A domain-specific language for stream parallelism.

- C3: Generalized transformation rules for source-to-source code generation that exploits parallelism in multi-core and cluster.

- C4: Experimental validation through the implementation of several different use cases to access features of the framework and design choices.

# 1.4 Outline

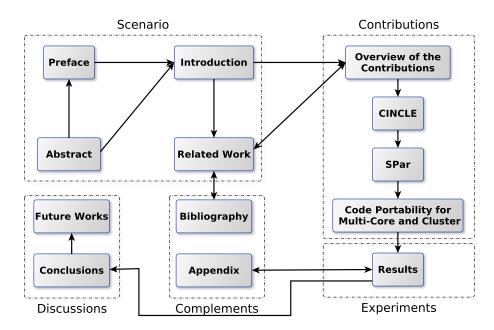

This dissertation is organized in five parts:

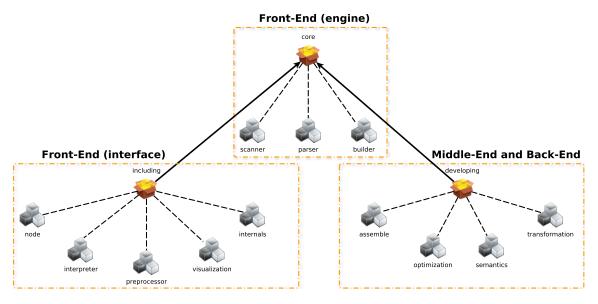

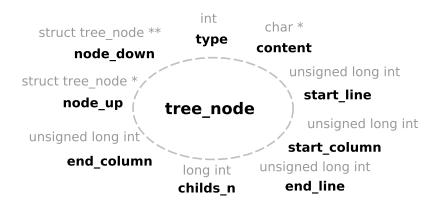

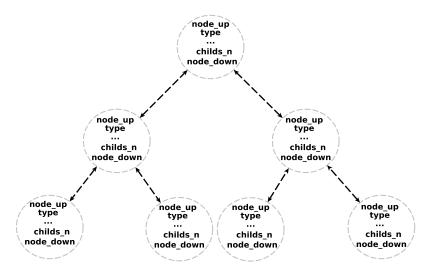

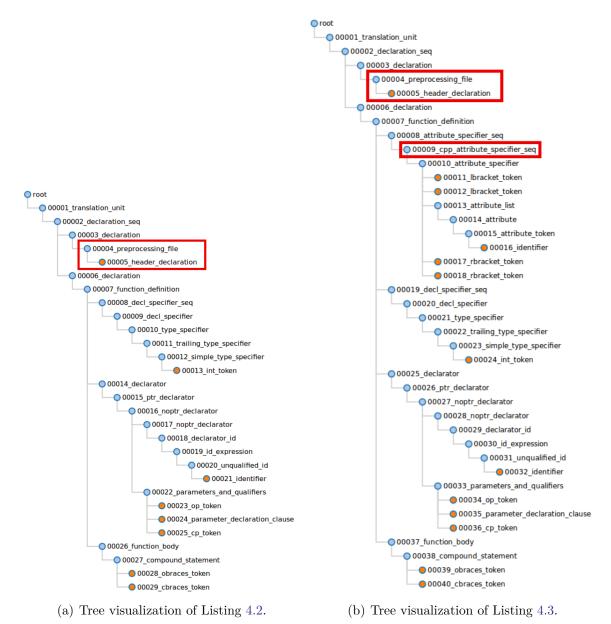

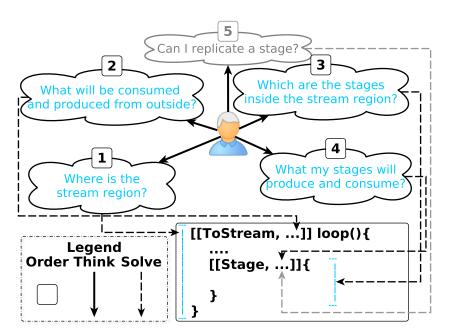

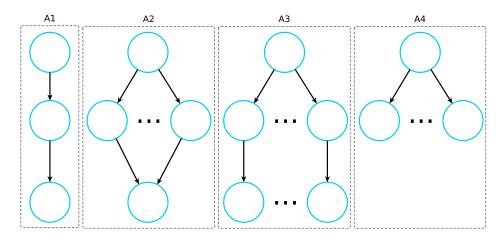

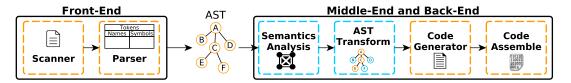

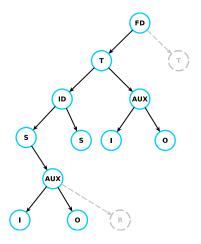

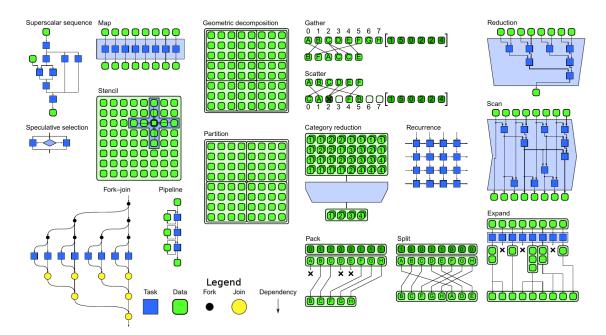

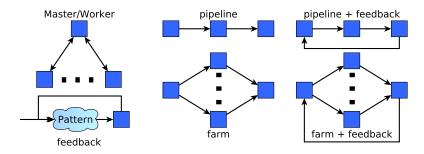

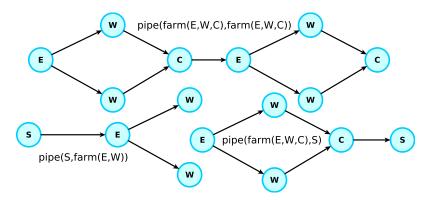

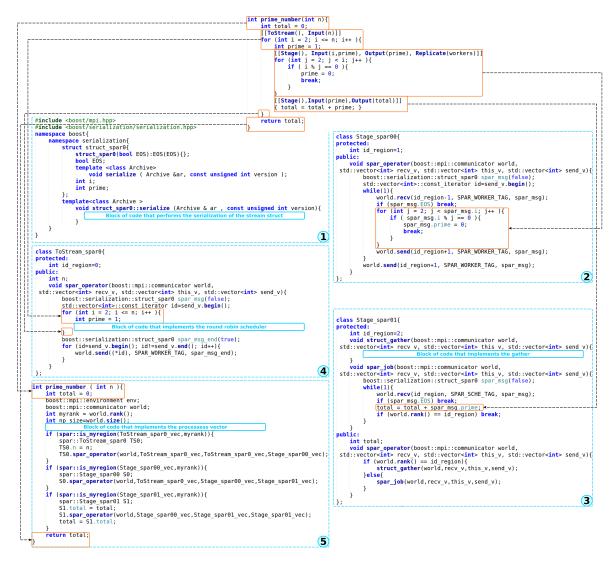

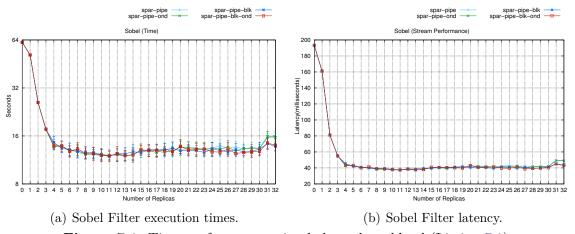

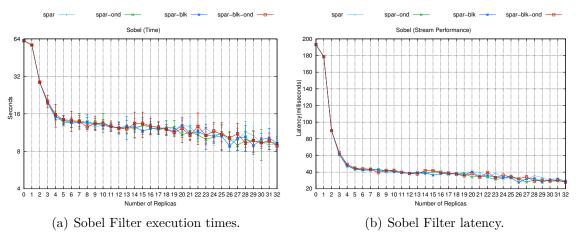

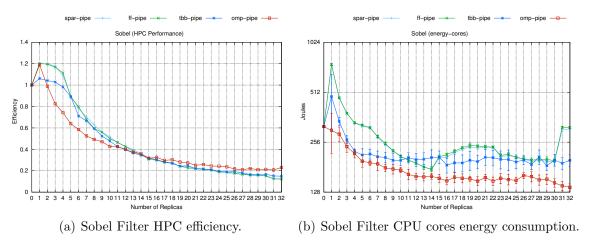

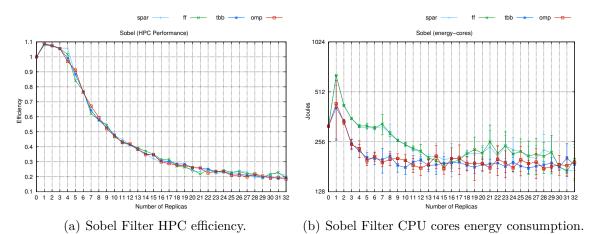

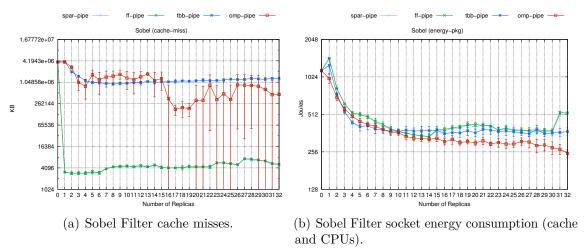

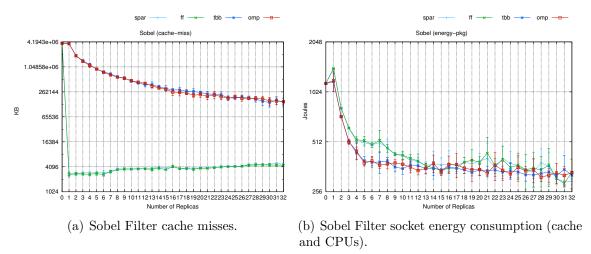

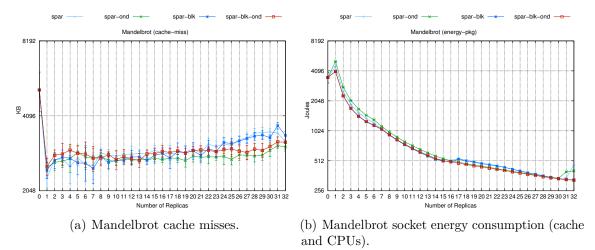

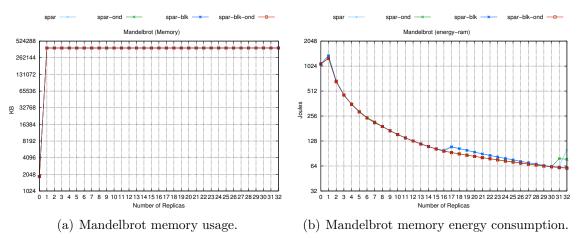

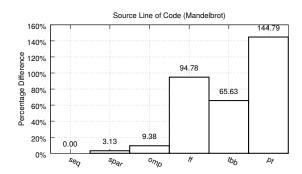

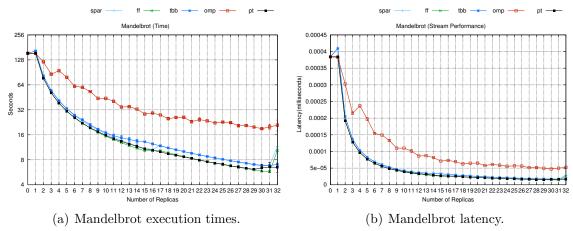

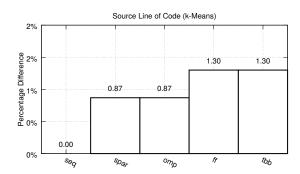

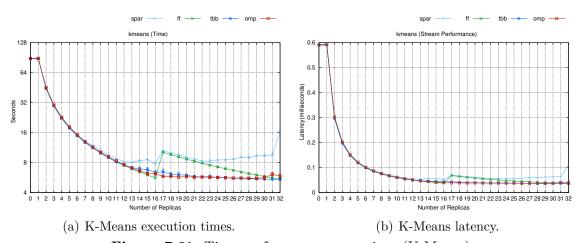

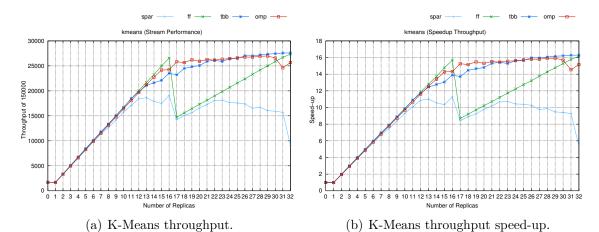

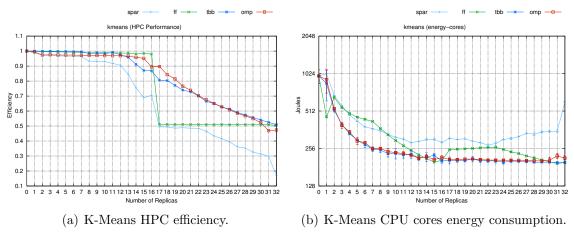

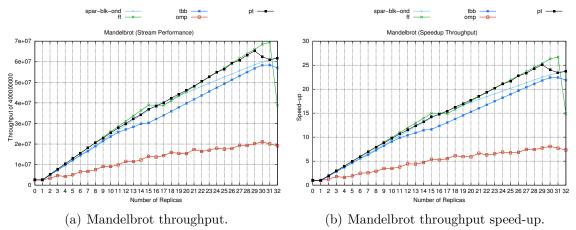

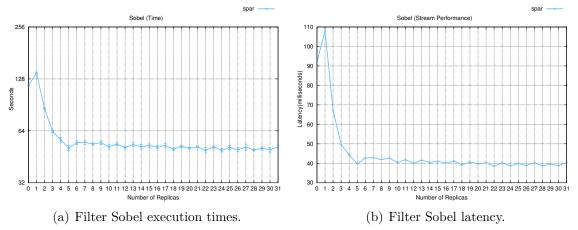

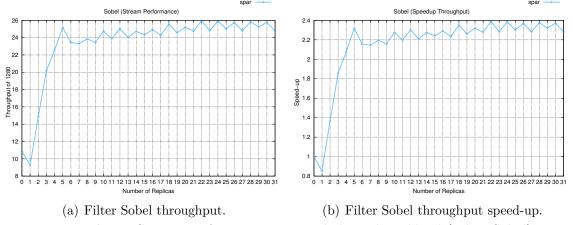

- Scenario: This part of the dissertation introduces the context, problems, challenges, and motivations in Chapter 1. Chapter 2 presents the related works to highlight the differences and similarities to our research.